您好!

我有一个长期困扰我的问题,关于 ePWM:

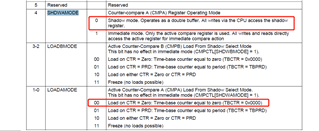

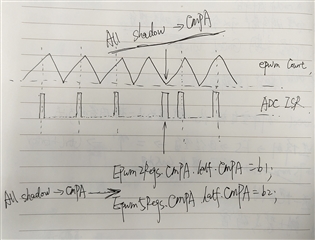

如上所示、高级表示 ADC ISR、如果我在此 ADC ISR 中的每个周期更新 PWM 寄存器值、并且我使用 PWM 比较影子寄存器、 C 代码就像这样:

interrupt void ADCISR(void)

{

....

EPwm1Regs.CMPA.half.CMPA = a1;

EPwm4Regs.CMPA.half.CMPA = a2;

EPwm2Regs.CMPA.half.CMPA = b1; //<------------------------

EPwm5Regs.CMPA.half.CMPA = b2;

EPwm3Regs.CMPA.half.CMPA = c1;

EPwm6Regs.CMPA.half.CMPA = c2;

...

}

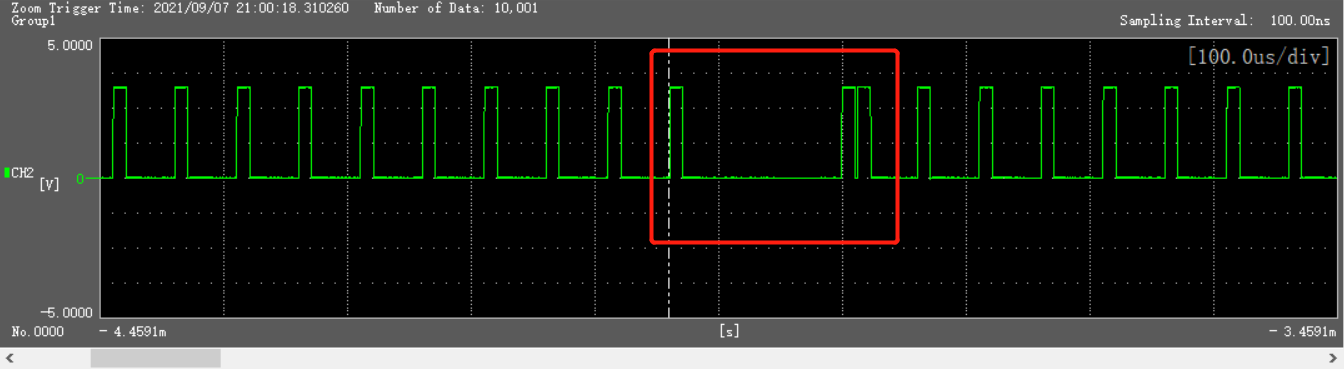

您可以看到 、ADC ISR 应严格执行一次、速度为50us、但由于 freemodbus 在处理数据帧时关闭了全局中断、因此 ADC ISR 延迟。 如红色框所示。

因此、在这种情况下、是否存在这样的可能性: 当 DSP 完成 “EPwm2Regs.CMPA.half.CMPA = B1;”后 ,PWM 将所有影子寄存器的值传输到 PWM 操作寄存器,这会导致“EPwm2Regs.CMPA.half.CMPA”的值成为新周期计算的结果,而“EPwm5Regs.CMPA.CMPA”的值仍是前一半周期计算结果。 如果这两个 PWM 控制同一电桥的上管和下管,是否可以 直接连接上桥和下桥?