我已经使用 CMPSS 和 ePWM DC+TZ 功能实现了斜坡补偿峰值电流控制器。

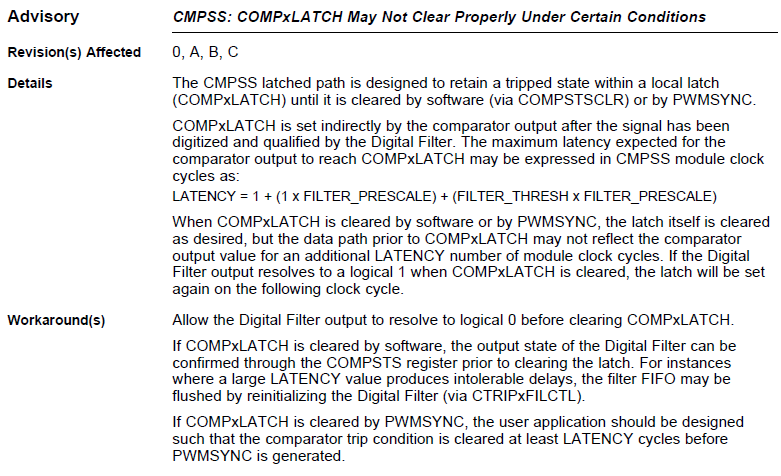

如上面的示波器捕获中所示、CBC 限制主要起作用、但偶尔会错过模拟比较事件、并且 ePWM 输出保持有效 (或立即恢复有效)、直到达到最大占空比(90%)。

事实证明、除非我将 DigitalCompareEventSyncMode 设置为"ePWM_DC_EVENT_INPUT_SYNCODED"、否则这种干扰的发生会很高。

启用同步后、干扰变得相当罕见、但仍然会发生。

下面是相关的初始化代码、希望提供一些有关可能发生的情况的线索。

感谢你的帮助。

心搏

{

SysCtl_enablePeripheral(SYSCTL_PERIPH_CLK_CMPSS2);

CMPSS_enableModule(CMPSS2_BASE);

CMPSS_configHighComparator(CMPSS2_BASE, CMPSS_INSRC_DAC);

// configuring ramp to 701599.121094 A/s (desired: 692307.692308 A/s)

CMPSS_configRamp(CMPSS2_BASE, 0, 11, 0, 5, true);

CMPSS_configDAC(CMPSS2_BASE, CMPSS_DACREF_VDDA | CMPSS_DACVAL_SYSCLK |

CMPSS_DACSRC_RAMP);

XBAR_setEPWMMuxConfig(XBAR_TRIP8, XBAR_EPWM_MUX02_CMPSS2_CTRIPH);

XBAR_enableEPWMMux(XBAR_TRIP8, XBAR_MUX02);

}

{

HRPWM_setSyncPulseSource(EPWM5_BASE, HRPWM_PWMSYNC_SOURCE_ZERO);

EPWM_setTripZoneDigitalCompareEventCondition(EPWM5_BASE,

EPWM_TZ_DC_OUTPUT_B2,

EPWM_TZ_EVENT_DCXH_HIGH);

EPWM_enableDigitalCompareTripCombinationInput(EPWM5_BASE,

EPWM_DC_COMBINATIONAL_TRIPIN8,

EPWM_DC_TYPE_DCBH);

EPWM_setDigitalCompareFilterInput(EPWM5_BASE,

EPWM_DC_WINDOW_SOURCE_DCBEVT2);

EPWM_setDigitalCompareBlankingEvent(EPWM5_BASE,

EPWM_DC_WINDOW_START_TBCTR_ZERO);

EPWM_setDigitalCompareWindowOffset(EPWM5_BASE, 0);

EPWM_setDigitalCompareWindowLength(EPWM5_BASE, 0);

EPWM_enableDigitalCompareBlankingWindow(EPWM5_BASE);

EPWM_setDigitalCompareEventSource(EPWM5_BASE,

EPWM_DC_MODULE_B,

EPWM_DC_EVENT_2,

EPWM_DC_EVENT_SOURCE_FILT_SIGNAL);

EPWM_setDigitalCompareEventSyncMode(EPWM5_BASE,

EPWM_DC_MODULE_B,

EPWM_DC_EVENT_2,

EPWM_DC_EVENT_INPUT_SYNCED);

EPWM_enableTripZoneSignals(EPWM5_BASE, EPWM_TZ_SIGNAL_DCBEVT2);

}