主题中讨论的其他器件: TMS320F28377D

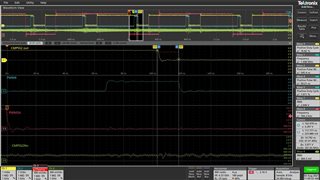

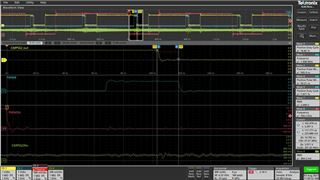

CMPSS2设置为通过 PWM4的 CMPC 进行斜升和复位,在这种情况下,CMPC 设置为5 (CMPA 也设置为5,控制 PWM4下降沿的发生位置,因此比较器应在 PWM4的每个下降沿复位)。 我们注意到、它将在每个周期的早期复位大约15ns。 我们在与问题1和问题2 (链接)相同的设置下观察到了这一点。 我们在 TMS320F28379D 评估卡和使用 TMS320F28377D 的定制硬件上都观察到了此问题。 CMPSS2+的输入为0.360V。 微控制器的时钟频率为20MHz、PLL 配置为产生200MHz 的系统时钟、PWM 时钟设置为100MHz。

最小工作代码为 attachede2e.ti.com/.../1222.minimal_5F00_working_5F00_example.zip