主题中讨论的其他器件:C2000WARE

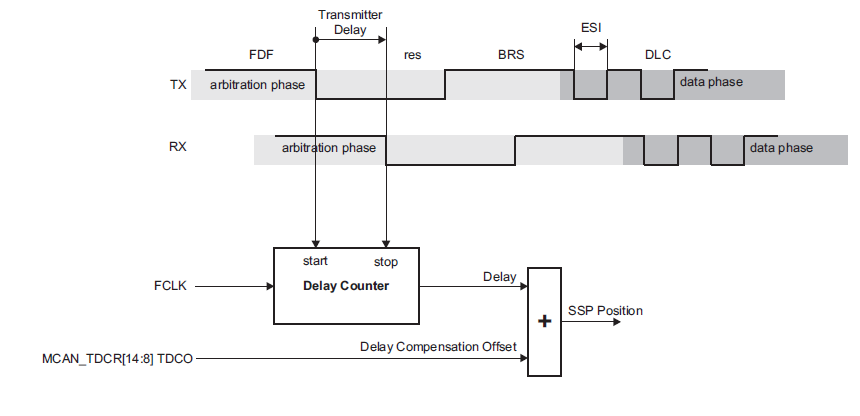

我正在尝试使 CANFD 工作、并且在发送和接收方向上都有1Mbps 组帧/2Mbps 数据工作。 但是、当我将数据速率提高到4Mbps 时、会出现许多 CAN 错误、而在8Mbps 时不会出现任何错误。 根据我的读数、我怀疑从 TX 侧到 RX 侧的传播延迟、TDCR 寄存器似乎会影响这些误差。 我已经阅读并重新阅读了这些 TDCO 和 TDCF 的说明、但仍有一些设置不清楚。

TDCO 是否更改 SSP、因此增大 TDCO 将延迟 TX 之后的 RX 测量?

TDCF 有什么作用? 我知道要发挥作用必须大于 TDCO、但其实际功能不清楚。

我认为我需要在 TX 之后延迟 RX 测量、因为我的 CAN 收发器延迟(对于显性 TX)最大值为170ns。 我曾尝试使用这些 TDCO 和 TDCF、但没有明显的改进。

谢谢、

Jim