主题中讨论的其他器件:REF5030、 TINA-TI

你(们)好

我将使用 ADC_Ex5_SoC_Continuous 示例测试28388 ADC。

基于控制卡的电路、使用 REF5030作为参考。

我在 ADCINB0 - GND、ADCINB0 - 3.3V 之间连接了两个1k Ω、以获得1.65V

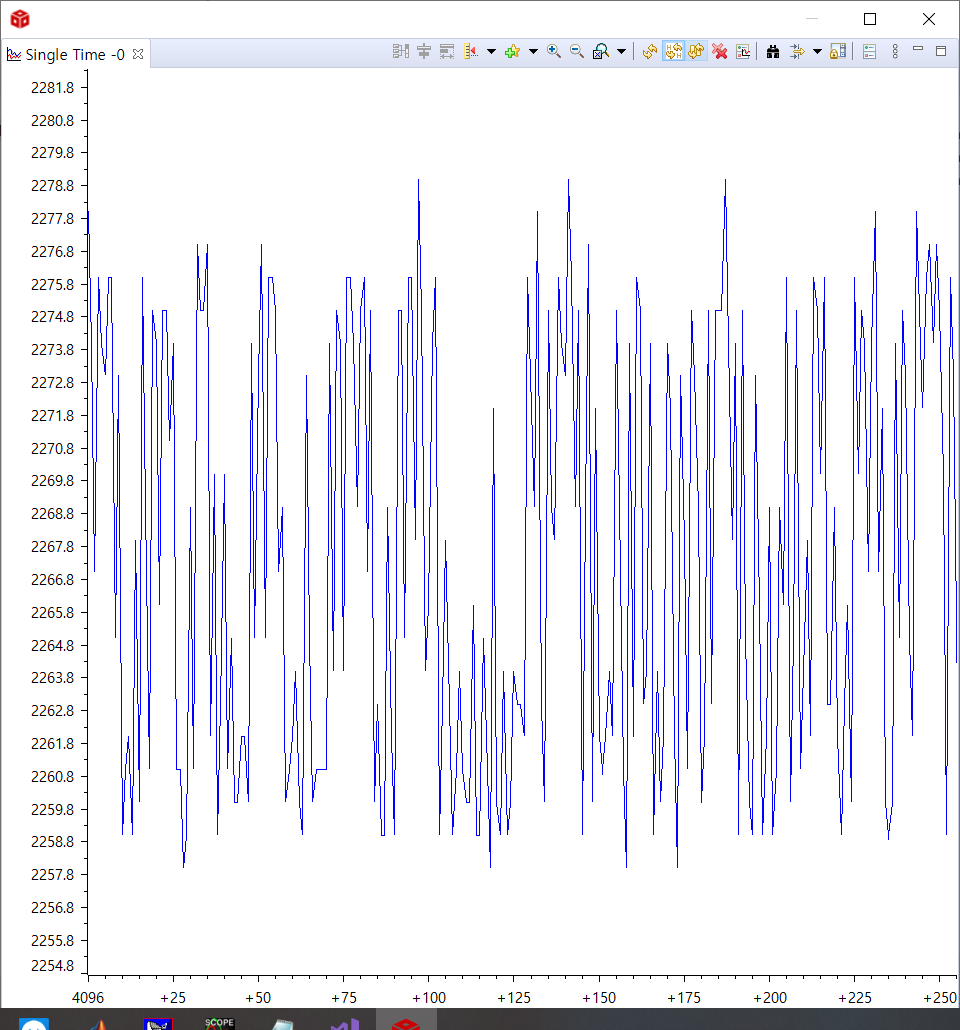

这是样本结果、大约20 LSB 波动。

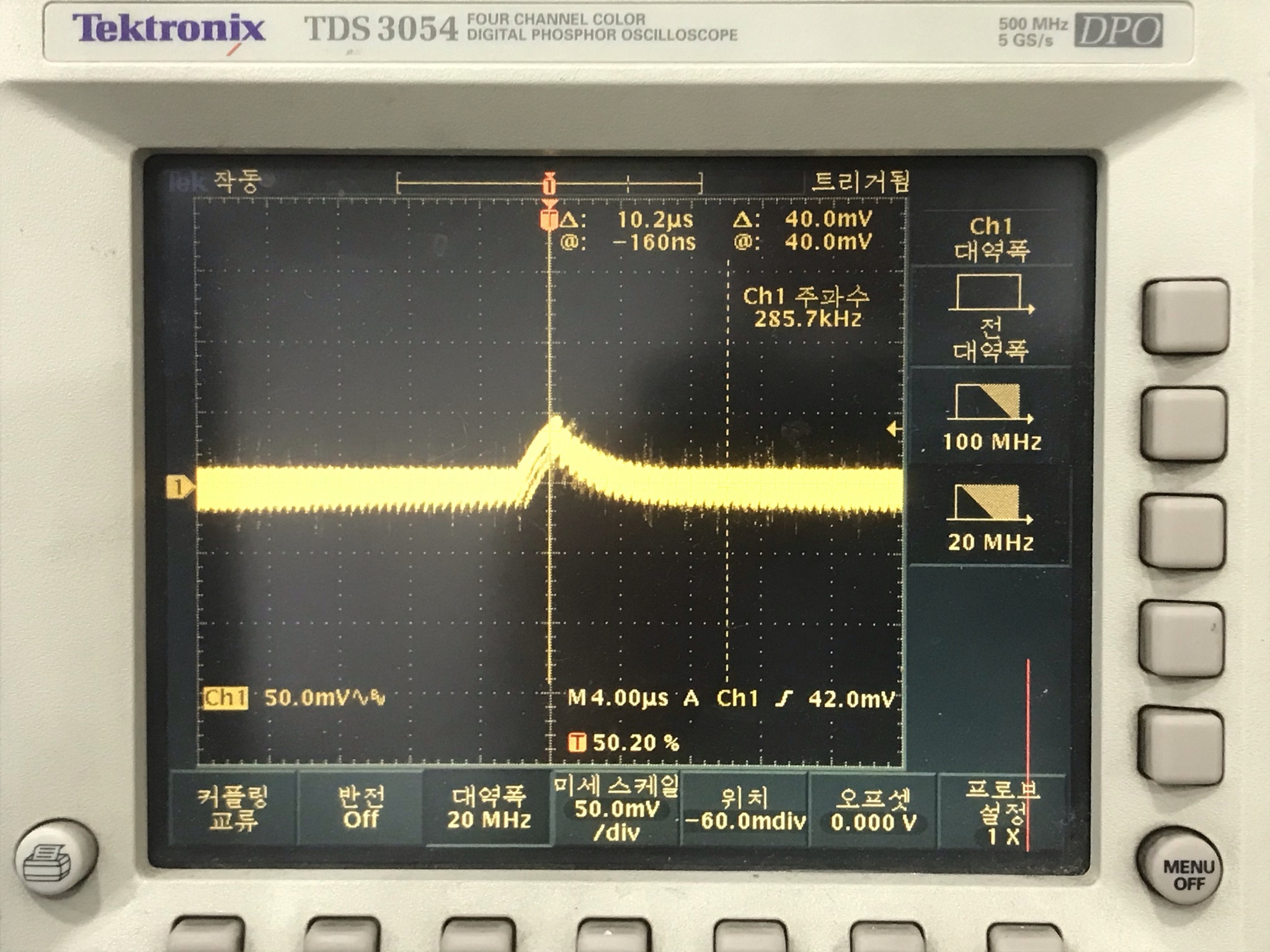

但我想知道为什么 ADCIN 引脚在示波器上跳转50mV

进行采样。 而3.3VA 和 ref 引脚在示波器上仍然保持干净。

我尝试了几个 acqps 8/63/125。 125看起来不错、但只有8个小于9 LSB 磁通、而另20 LSB。

它是否可预测的正常现象?

是否有任何方法可以改进它?

此致

金泰荣