主题中讨论的其他器件:ADS8684、 ADS8684A

大家好、

我正在使用 F28379D 进行一个项目、我有一个具有我需要的所有外设(PWM、ADC...)的项目 我目前正在设计使用外部 ADC (ADS8684)的 SPI 通信。

我设计了我所需的所有功能、我的 SPI 看起来不错(我还没有 ADS8684A、所以我只使用示波器查看 SPI 总线的信号)。

为了优化我的代码、我想查看程序中时间计算的宽松位置。 我做了一些测试、事实是我的 SPI 花费了很多时间...

这是我的问题:

我不明白为什么我的指令 GPIO_WRITE (32、0)和 SPI_writeData 之间的时间超过500ns ...

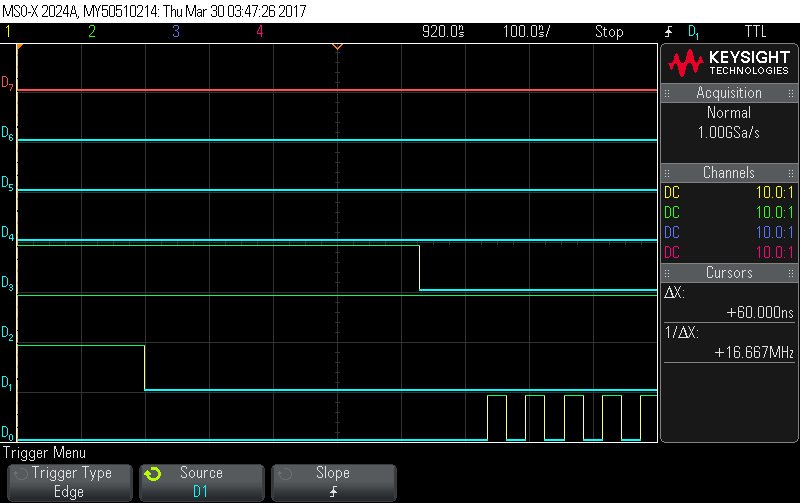

下面是我的振荡器的捕捉(D0是 SPIA 的 CLK 信号;D1是 GPIO 32;D3是 SPIA 的 CS 信号)

以下是我的说明:

下面是 SPIA 的配置:

我再次精确地确定、我的 SPI 暂时未连接任何设备、我认为这不是问题、但我精确地说...

提前感谢您的回答!

纪尧姆