各位专家、您好!

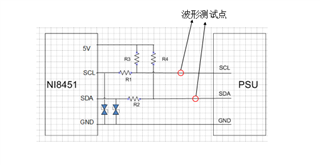

我的客户发现在 执行 I2C 测试时、SCL 信号在低电平下拉0.2V、 然后恢复。 它们使用 TMS320F28069作为从器件、使用 NI8451作为主机、该接口 如下所示:

测试结果为:

读取00h 与 NI8451、数据为 B2h、00h、B3h、00h、(PEC)

波形记录如下:CH1:SCL、CH2:SDA、CH3:调试

(1)下图显示了命令00h 波形、该波形在从器件响应 ACK 信号前后的低 SCL 电平期间被下拉约0.2V;

(2) SlaveAddr+R (B3h)波形、在从器件响应 ACK 信号之前和之后的低 SCL 电平期间被拉低、ACK 周期之后的时间越长、主机读取数据、从器件未就绪(I2CXSR 为空。 然而、I2CDXR 尚未写入数据)、并且 SCL 被从器件下拉。

(3)从机应答数据00h 波形、每次从机应答数据时、SCL 低电平被下拉;

您知道什么是根本原因吗? 谢谢!