您好!

以下问题描述了我遇到的问题 以及导致我采取变通办法的调查。 我想知道我的推理是否正确,解决办法是否能够证明未来的情况。

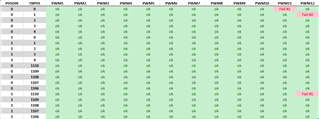

我的设计使用 DSP 的全部12个 ePWM。 它分为2组配置、每个组具有一个生成同步信号的主器件。 PWM1与 PWM2同步到6、PWM7是 PWM 8至12的主器件。 所有从 器件都启用了相位控制(PHSEN = 1)。 要获得此配置、SYNCSELEPWM10SYNCIN = 2

我最近开始看到一些装置出现异常故障、而设计现在已经稳定了多年。 在随机模式下、PWM11或 PWM12输出将产生长脉冲。 我的 CPU 以200MHz、TBPRD=1110的频率运行、在上-下模式下工作、提供90KHz 的方波输出和稳定的50%占空比。 很多时候、输出会"跳过一个脉冲"、从而产生一个150%的脉冲。

经过调查,我 收集了所有这些事实

- 这只会在 PWM11和 PWM12上发生

- 故障模式仅在 以下条件下发生(其他经测试的值和行为稳定)

- 方向为低(PHSDIR=0)、相位值为0或1 (TBPHS=0、1)

- 方向为向上(PHSDIR=1)、相位为1110 (TBPHS=TBPRD)。

- 故障与 其他 PWM 模块的 CPMA、CMPB、TBPHS 寄存器的配置方式无关。

- 所有发生故障的设备都具有相同的 DSP 技术支持代码:YFC-94A9RPW

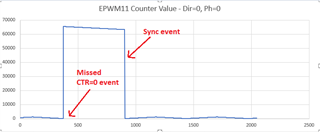

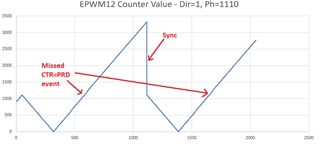

进一步推动调查、我开始在问题发生时监控计数器的行为。 我看到的是2种故障模式

向上向下计数模式似乎错过了 CTR=0或 CTR=PRD 事件、并将继续在超出范围[0-1110]的情况下计数、直至发生下一个同步事件。

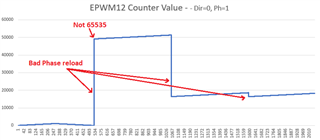

2.第二种故障模式更令人担忧。 发生同步事件时、TBCTR 寄存器中加载的相位值看起来是随机的。 请记住、计数器应保持在0和1110内。

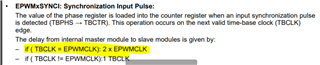

在手册中、我发现了这种说法

结论

在以上所有陈述中、我感觉定时器模块中存在某种比赛状态。

就像时基模块在到达0时将计数方向从向下翻转为向上、但同步事件随后将方向重新变为向下、而不让时基模块第二次做出反应、而计时器将继续以负值(65535和更低)运行。 假设是这种情况、我可以根据 [2.1108]之间的方向轻松使相位寄存器饱和。

这种解决方案确实解决了所有问题、但我无法用这种推理来解释第二种故障模式、这让我对我使用的解决方案充满怀疑。 如果我在一个真正的硬件异步竞争条件之前、这是有道理的、但是由于我正在处理一个同步设计、所以我无法解释"随机"相位重新加载值。 但是、与一批芯片相关的事实让我认为它可能是一个异步竞争条件。

在这里、我需要 TI 的帮助来评估应对这种情况的正确方法。

非常感谢