尊敬的香榭丽舍

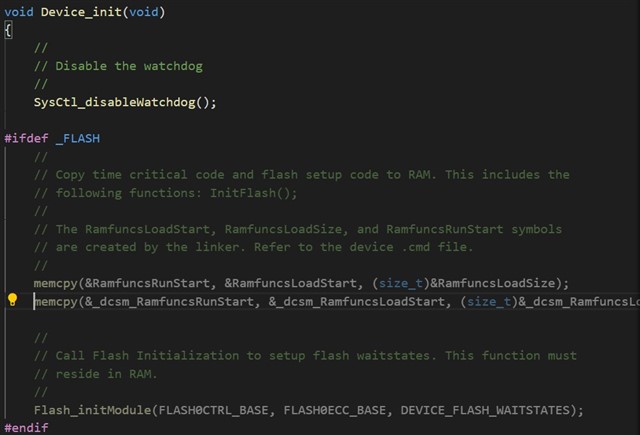

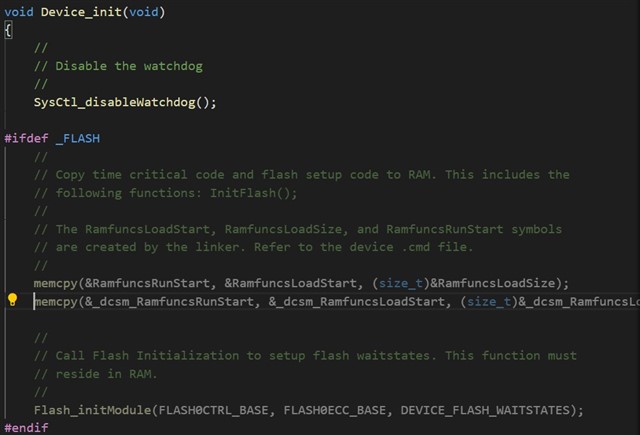

客户尝试将要从 DCSM 中的安全区域运行的代码复制到正常闪存部分、但遇到崩溃结果。

它们通过 DCSM 在安全闪存中配置了“Device_init”,但当在 Flash_initModule (在 RAMGSx 中)中运行时,CPU 遇到崩溃。

有人对此问题有任何建议吗? 因为我们可以 在 F2837x 中使用此方法、但在 F2838x 中始终无法崩溃。

如果您有任何建议、请随时告诉我。

非常感谢。

此致、

Janet

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

尊敬的香榭丽舍

客户尝试将要从 DCSM 中的安全区域运行的代码复制到正常闪存部分、但遇到崩溃结果。

它们通过 DCSM 在安全闪存中配置了“Device_init”,但当在 Flash_initModule (在 RAMGSx 中)中运行时,CPU 遇到崩溃。

有人对此问题有任何建议吗? 因为我们可以 在 F2837x 中使用此方法、但在 F2838x 中始终无法崩溃。

如果您有任何建议、请随时告诉我。

非常感谢。

此致、

Janet

Janet、您好!

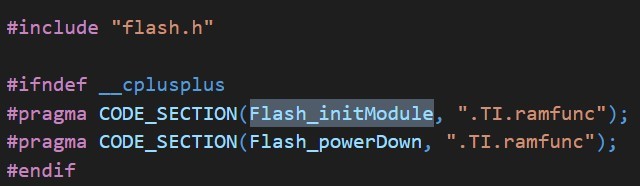

因此、在这种情况下、客户将某些函数(闪存初始化)从安全闪存复制到非安全 RAM。 正确? 如果是,您能否确认 memcpy 函数的位置? 这应该位于安全存储器中、以便能够从安全闪存复制数据。 请参阅本 应用手册中的"使用 RTS 库中的 memcpy 函数"部分 、了解有关此内容的更多详细信息。

接下来要检查的是闪存扇区的安全配置。 如果同时使用两个区域、则配置值存在一些差异。 如果仅使用一个区域、则 只要其他区域不安全(由 BootROM 代码针对默认密码完成)、这一点就无关紧要。

此致、

Vivek Singh

尊敬的 Vivek:

是的、我们在 flash2 (地址0x0008285D)中检查了 memcpy (rts2800_fpu64_eabi.lib)、即使我们尝试使用循环代码将代码复制到全局 RAM、它仍会在跳转到 Flash_initModule 函数时崩溃。

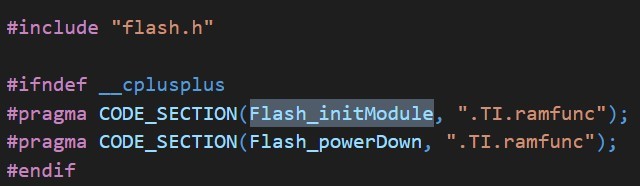

我们 尝试了一个示例、如下 所示。 在本例中、 我们尝试通过 DCSM 使闪存中的所有代码安全。 在 DCSM 之后、这个代码将不起作用、持续触发复位(XRS)并且重新启动。 希望此代码对本主题有所帮助。

#include "device.h"

#include "driverlib.h"

#define ON 1

#define OFF 0

#define GPIO_PIN_LED_RED 34

void Init_GPIO(void)

{

//

// Enable a GPIO output on GPIO6, set it high

//

GPIO_setPadConfig(GPIO_PIN_LED_RED, GPIO_PIN_TYPE_PULLUP); // Enable pullup on GPIO6

GPIO_writePin(GPIO_PIN_LED_RED, ON); // Load output latch

GPIO_setPinConfig(GPIO_34_GPIO34); // GPIO6 = GPIO6

GPIO_setDirectionMode(GPIO_PIN_LED_RED, GPIO_DIR_MODE_OUT); // GPIO6 = output

}

void delayMS(uint32_t t) {

int i;

for(i=0;i<t;++i) {

DEVICE_DELAY_US(1000);

}

}

int main(void)

{

//

// Initialize device clock and peripherals

//

Device_init();

//

// Disable pin locks and enable internal pull-ups.

//

Device_initGPIO();

//

// Initialize PIE and clear PIE registers. Disables CPU interrupts.

//

Interrupt_initModule();

//

// Initialize the PIE vector table with pointers to the shell Interrupt

// Service Routines (ISR).

//

Interrupt_initVectorTable();

//

// Initialize other function

//

Init_GPIO();

while(1) {

GPIO_writePin(GPIO_PIN_LED_RED, ON);

delayMS(500);

GPIO_writePin(GPIO_PIN_LED_RED, OFF);

delayMS(500);

}

return 0;

}

MEMORY

{

/* BEGIN is used for the "boot to Flash" bootloader mode */

BEGIN : origin = 0x080000, length = 0x000004

BOOT_RSVD : origin = 0x000002, length = 0x0001AE /* Part of M0, BOOT rom will use this for stack */

RAMM0 : origin = 0x0001B0, length = 0x000250

RAMM1 : origin = 0x000400, length = 0x000400 /* on-chip RAM block M1 */

RAMD0_1 : origin = 0x00C000, length = 0x001000

RAMLS0_1 : origin = 0x008000, length = 0x001000

RAMLS2_7 : origin = 0x009000, length = 0x003000

RAMGS0_15 : origin = 0x00D000, length = 0x010000

/* Flash sectors */

FLASH0_4 : origin = 0x080004, length = 0x00FFFC /* on-chip Flash */

FLASH5_8 : origin = 0x090004, length = 0x01FFFC /* on-chip Flash */

FLASH9_12 : origin = 0x0B0000, length = 0x00E000 /* on-chip Flash */

FLASH13 : origin = 0x0BE000, length = 0x002000 /* on-chip Flash */

CPU1TOCPU2RAM : origin = 0x03A000, length = 0x000800

CPU2TOCPU1RAM : origin = 0x03B000, length = 0x000800

CPUTOCMRAM : origin = 0x039000, length = 0x000800

CMTOCPURAM : origin = 0x038000, length = 0x000800

CANA_MSG_RAM : origin = 0x049000, length = 0x000800

CANB_MSG_RAM : origin = 0x04B000, length = 0x000800

RESET : origin = 0x3FFFC0, length = 0x000002

}

SECTIONS

{

codestart : > BEGIN ,PAGE = 0, ALIGN(4)

.text : >> FLASH0_4,PAGE = 0, ALIGN(4)

.cinit : > FLASH0_4,PAGE = 0, ALIGN(4)

.switch : > FLASH0_4, PAGE = 0,ALIGN(4)

.reset : > RESET, TYPE = DSECT /* not used, */

.stack : > RAMD0_1

dcsm_data_section : > RAMLS2_7 PAGE = 0

#if defined(__TI_EABI__)

.init_array : > FLASH0_4, ALIGN(4)

.bss : > RAMGS0_15

.bss:output : > RAMGS0_15

.bss:cio : > RAMGS0_15

.data : > RAMGS0_15

.sysmem : > RAMGS0_15

/* Initalized sections go in Flash */

.const : > FLASH0_4, ALIGN(4)

#else

.pinit : > FLASH1, ALIGN(4)

.ebss : > RAMLS5

.esysmem : > RAMLS5

.cio : > RAMLS5

/* Initalized sections go in Flash */

.econst : >> FLASH4 | FLASH5, ALIGN(4)

#endif

MSGRAM_CPU1_TO_CPU2 : > CPU1TOCPU2RAM, type=NOINIT

MSGRAM_CPU2_TO_CPU1 : > CPU2TOCPU1RAM, type=NOINIT

MSGRAM_CPU_TO_CM : > CPUTOCMRAM, type=NOINIT

MSGRAM_CM_TO_CPU : > CMTOCPURAM, type=NOINIT

#if defined(__TI_EABI__)

.TI.ramfunc : {} LOAD = FLASH0_4,

RUN = RAMGS0 | RAMGS1 | RAMGS2 |RAMGS3,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(4)

#else

.TI.ramfunc : {} LOAD = FLASH3,

RUN = RAMLS0 | RAMLS1 | RAMLS2 |RAMLS3,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

ALIGN(4)

#endif

}

.sect "dcsm_z1otp_link_pointer"

.retain

.long 0x00003FFF ;Z1OTP_LINKPOINTER1

.long 0x00003FFF ;Z1OTP_LINKPOINTER2

.long 0x00003FFF ;Z1OTP_LINKPOINTER3

.sect "dcsm_z1otp_jlm_enable"

.retain

.long 0xFFFF000F ;Z1OTP_JLM_ENABLE

.sect "dcsm_z1otp_gpreg"

.retain

.long 0xFFFFFFFF ;Z1OTP_GPREG1

.long 0xFFFFFFFF ;Z1OTP_GPREG2

.long 0xFFFFFFFF ;Z1OTP_GPREG3

.long 0xFFFFFFFF ;Z1OTP_GPREG4

.sect "dcsm_z1otp_pswd_lock"

.retain

.long 0x007FFFFF ;Z1OTP_PSWDLOCK

.sect "dcsm_z1otp_crc_lock"

.retain

.long 0x7FFFFFFF ;Z1OTP_CRCLOCK

.sect "dcsm_z1otp_jtag_pswdh"

.retain

.long 0x4bFFFFFF ;Z1OTP_JTAGPSWDH0

.long 0x3FFFFFFF ;Z1OTP_JTAGPSWDH1

.sect "dcsm_z1otp_cmac_key"

.retain

.long 0xFFFFFFFF ;Z1OTP_CMACKEY0

.long 0xFFFFFFFF ;Z1OTP_CMACKEY1

.long 0xFFFFFFFF ;Z1OTP_CMACKEY2

.long 0xFFFFFFFF ;Z1OTP_CMACKEY3

.sect "dcsm_zsel_z1"

.retain

.long 0x87654321 ;Z1OTP_CSMPSWD0 (LSW of 128-bit password)

.long 0x4D770000 ;Z1OTP_CSMPSWD1

.long 0x12345678 ;Z1OTP_CSMPSWD2

.long 0x19916140 ;Z1OTP_CSMPSWD3 (MSW of 128-bit password)

.long 0x05555555 ;Z1OTP_GRABSECT1 CPU1 flash : ALL

.long 0x0FFFFFFF ;Z1OTP_GRABSECT2 CM core

.long 0x0FFFFFFF ;Z1OTP_GRABSECT3 CPU2 flash

.long 0x00055555 ;Z1OTP_GRABRAM1

.long 0xFFFFFF0F ;Z1OTP_GRABRAM2

.long 0x000FFFFF ;Z1OTP_GRABRAM3

;; .long 0x3FFF3FFF ;Z1OTP_EXEONLYSECT1

;; .long 0x00003FFF ;Z1OTP_EXEONLYSECT2

;; .long 0xFFC303FF ;Z1OTP_EXEONLYRAM1

;; .long 0xFFFFFFFF ;Reserved

;; .long 0xFFFFFFFF ;Z1OTP_JTAGPSWDL0

;; .long 0x27FFFFFF ;Z1OTP_JTAGPSWDL1

此致、

Kenny Jhan

这是奇怪的、因为如果代码没有被复制、那么 CPU 应该保持在闪存设置函数内。 在这种情况下、将发生 ITRAP、CPU 将跳转到 BootROM 中的 ITRAP 处理程序。

您能否执行以下步骤-

在 CPU 在断点处暂停后、打开内存监视窗口中的 GSRAM 位置、查看是否复制了任何数据。

此致、

Vivek Singh

尊敬的 Vivek:

我认为有问题。 当我解锁 DCSM 时、它保持在 RAMGS0中。 我的详细步骤如下:

1. 下载代码并重新启动开发板

2. (现在、XRS 连续触发) 拉低 GPIO72 以保持等待引导模式

3. 打开 CCS 和 lanch 芯片

4. 连接 C28xx_CPU1和加载符号

5.按下图标"CPU Reset"(在地址"0x3fd2ae"处中断、没有可用的调试信息、或者在程序代码之外)

6. 打开"存储器浏览器"、将地址切换到0xD00并写入0B5A

7.打开"Memory Map"->"on-Chop Flash"

8。 键入 CSMPSWD 并解锁(在地址"0xd058"处中断、没有可用的调试信息、或在程序代码之外中断。)

9. 在函数 Flash_initModule 处设置硬件断点

10.按下图标"Resume"(恢复)(在地址"0x3fe96f"处中断、没有可用的调试信息、或者在程序代码之外。) --> ESTOP0

11.在 "存储器浏览器"中打开 RAMGS0位置(0xD000)、数据全部为0x0000

此致、

Kenny Jhan

您好!

[引用 userid="486178" URL"~/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/996161/tms320f28388d-copy-code-from-dcsm-secure-zone-to-un-secure-zone/3698069 #3698069"]8. 键入 CSMPSWD 并解锁(在地址"0xd058"处中断、没有可用的调试信息、或在程序代码之外中断)您应该使用 CCS 寄存器视图输入密码、而不是通过 CCS 片上闪存插件 GUI 输入密码、因为在加载程序之前使用了该 GUI。

此外、如果您看看我提到的步骤、我请求您只输入 KEY0和 key1 (64位值)来解锁 ECSL、而不是完全安全。 请尝试正确的步骤并告诉我结果。

此致、

Vivek Singh

尊敬的 Vivek:

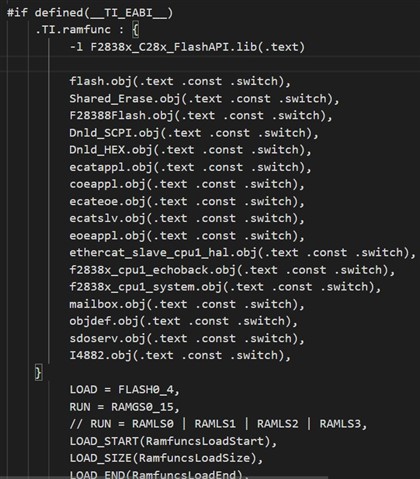

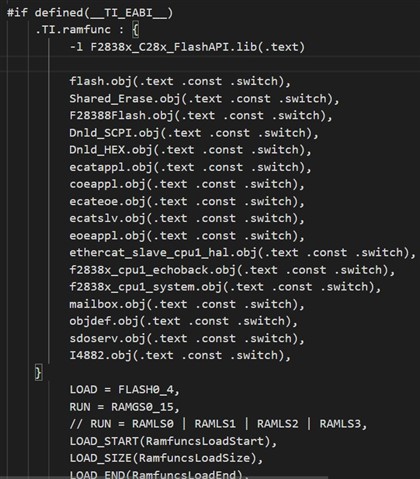

结果可能是肯定的...但是如果我更改了在 RAMLS0_1中运行的.TI.ramfunc (现在在 RAMGS0_15中运行) ,它将运行良好,cmd 文件如下(输出格式为 eabi)。 我尝试删除.TI.ramfunc 段中的函数。 它也起作用。

MEMORY

{

/* BEGIN is used for the "boot to Flash" bootloader mode */

BEGIN : origin = 0x080000, length = 0x000004

BOOT_RSVD : origin = 0x000002, length = 0x0001AE /* Part of M0, BOOT rom will use this for stack */

RAMM0 : origin = 0x0001B0, length = 0x000250

RAMM1 : origin = 0x000400, length = 0x000400 /* on-chip RAM block M1 */

RAMD0_1 : origin = 0x00C000, length = 0x001000

RAMLS0_1 : origin = 0x008000, length = 0x001000

RAMLS2_7 : origin = 0x009000, length = 0x003000

RAMGS0_15 : origin = 0x00D000, length = 0x010000

/* Flash sectors */

FLASH0_4 : origin = 0x080004, length = 0x00FFFC /* on-chip Flash */

FLASH5_8 : origin = 0x090004, length = 0x01FFFC /* on-chip Flash */

FLASH9_12 : origin = 0x0B0000, length = 0x00E000 /* on-chip Flash */

FLASH13 : origin = 0x0BE000, length = 0x002000 /* on-chip Flash */

CPU1TOCPU2RAM : origin = 0x03A000, length = 0x000800

CPU2TOCPU1RAM : origin = 0x03B000, length = 0x000800

CPUTOCMRAM : origin = 0x039000, length = 0x000800

CMTOCPURAM : origin = 0x038000, length = 0x000800

CANA_MSG_RAM : origin = 0x049000, length = 0x000800

CANB_MSG_RAM : origin = 0x04B000, length = 0x000800

RESET : origin = 0x3FFFC0, length = 0x000002

}

SECTIONS

{

codestart : > BEGIN ,PAGE = 0, ALIGN(4)

.text : >> FLASH0_4,PAGE = 0, ALIGN(4)

.cinit : > FLASH0_4,PAGE = 0, ALIGN(4)

.switch : > FLASH0_4, PAGE = 0,ALIGN(4)

.reset : > RESET, TYPE = DSECT /* not used, */

.stack : > RAMD0_1

dcsm_data_section : > RAMLS2_7 PAGE = 0

#if defined(__TI_EABI__)

.init_array : > FLASH0_4, ALIGN(4)

.bss : > RAMGS0_15

.bss:output : > RAMGS0_15

.bss:cio : > RAMGS0_15

.data : > RAMGS0_15

.sysmem : > RAMGS0_15

/* Initalized sections go in Flash */

.const : > FLASH0_4, ALIGN(4)

#else

.pinit : > FLASH1, ALIGN(4)

.ebss : > RAMLS5

.esysmem : > RAMLS5

.cio : > RAMLS5

/* Initalized sections go in Flash */

.econst : >> FLASH4 | FLASH5, ALIGN(4)

#endif

MSGRAM_CPU1_TO_CPU2 : > CPU1TOCPU2RAM, type=NOINIT

MSGRAM_CPU2_TO_CPU1 : > CPU2TOCPU1RAM, type=NOINIT

MSGRAM_CPU_TO_CM : > CPUTOCMRAM, type=NOINIT

MSGRAM_CM_TO_CPU : > CMTOCPURAM, type=NOINIT

#if defined(__TI_EABI__)

.TI.ramfunc : {} LOAD = FLASH0_4,

RUN = RAMGS0_15,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(4)

#else

.TI.ramfunc : {} LOAD = FLASH3,

RUN = RAMLS0 | RAMLS1 | RAMLS2 |RAMLS3,

LOAD_START(_RamfuncsLoadStart),

LOAD_SIZE(_RamfuncsLoadSize),

LOAD_END(_RamfuncsLoadEnd),

RUN_START(_RamfuncsRunStart),

RUN_SIZE(_RamfuncsRunSize),

RUN_END(_RamfuncsRunEnd),

ALIGN(4)

#endif

}

/*

//===========================================================================

// End of file.

//===========================================================================

*/

此致、

Kenny Jhan