尊敬的团队:

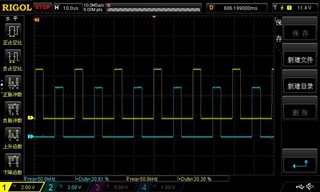

我的一个客户端 希望生成 PWM 波形、如下图所示:

他希望:

AQCTLA 寄存器在时基计数值为0时将 epwmA 设置为高电平、在时基计数值为 CMPA 时将 epwmA 设置为低电平;

AQCTLB 寄存器在时基计数值为 PRD 时将 epwmB 置为高电平、在时基计数值为 CMPB 时将 epwmB 置为低电平。

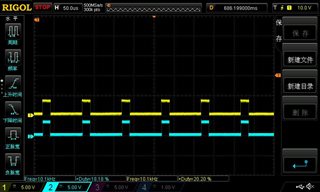

但最终会生成频率、占空比和相位相同的 PWM 波、如下图:所示

我是否可以询问此设置有什么问题? 下面是他的代码:

初始化部分:

EPwm1Regs.TBPRD = p->PERIOD;

EPwm1Regs.TBPHS.all = 0;

EPwm1Regs.TBCTR = 0x0000;

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN; //递增递减计数模式

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; //禁止TBPHS加载到TBCTR

EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm1Regs.EPWMSYNCINSEL.all = 0;

EPwm1Regs.EPWMSYNCOUTEN.all = 0;

EPwm1Regs.TBCTL2.bit.OSHTSYNCMODE = 0;

EPwm1Regs.TBCTL.bit.CLKDIV = 0; //时间基准时钟预分频位

EPwm1Regs.TBCTL.bit.HSPCLKDIV = 0; //高速时间基准时钟预分频位

EPwm1Regs.TBCTL.bit.FREE_SOFT = 11;

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

EPwm1Regs.AQCTL.bit.SHDWAQAMODE = 0;

EPwm1Regs.AQCTL.bit.SHDWAQBMODE = 0;

EPwm1Regs.AQCTLA.bit.ZRO = AQ_SET;

EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.PRD = AQ_SET;

EPwm1Regs.AQCTLB.bit.CBD = AQ_CLEAR;

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE;

/*====================================================================*/

EPwm1Regs.CMPA.bit.CMPA = p->CMPRA;

EPwm1Regs.CMPB.bit.CMPB = p->CMPRB;

/*====================================================================*/

EALLOW;

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 1;

EDIS;

PWM 信号:

EPwm1Regs.AQCTLA.bit.ZRO = AQ_SET;

EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR;

EPwm1Regs.AQCTLB.bit.PRD = AQ_SET;

EPwm1Regs.AQCTLB.bit.CBD = AQ_CLEAR;

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE;

EPwm1Regs.DBFED.all = 100;

EPwm1Regs.DBRED.all = 100;

EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HI;

EPwm1Regs.AQCSFRC.bit.CSFA = 0;

EPwm1Regs.AQCSFRC.bit.CSFB = 0;

此致