现在在我的项目中,我使用 CLA,但我有一个程序,我使用 PWM7 TBCTR=CMPB 作为 CLA 触发器,我可以进入 CLA 代码运行,但我发现所有 PWMx.TBPRD=0xFFFF (初始值不是0xFFFF)

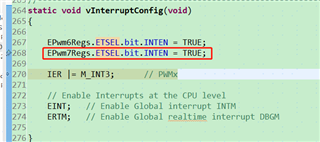

因此、我尝试通过阶跃调试来找出原因、然后我找到当单步执行"EPwm7Regs.ETSEL.bit.inten = true;"以及 所有 PWMx.TBPRD=0xFFFF 时的情况

这是我的 PWM7触发器初始代码: 原因是什么? 谢谢!

/ /

// ePWM 模块7配置:用于 ISR 和 ADC 触发

EPwm7Regs.TBPRD = PWM_INTPRD;//20160121更改为45k ISR 频率!!

EPwm7Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN;//向上计数/dn

EPwm7Regs.TBCTL.bit.PHSEN = TB_ENABLE;//从机模块

EPwm7Regs.TBCTL.bit.PHSDIR = TB_UP;

EPwm7Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm7Regs.TBPHS.bit.TBPHS = 2;

EPwm7Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_DISABLE;//禁用同步输出

//TBCLK=SYSCLKOUT/(HSPCLKDIV * CLKDIV)=SYSCLKOUT

EPwm7Regs.TBCTL.bit.CLKDIV = TB_DIV1;//时基时钟预分频

EPwm7Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;//高速时间预分频

EPwm7Regs.CMPB.bit.CMPB = INT_CMPB;

EPwm7Regs.ETSEL.bit.INTSEL = ET_CTRL_CMPB;

EPwm7Regs.ETSEL.bit.INTEN = 0;//禁用 INT

EPwm7Regs.ETPS.bit.INTPRD = et_1st;//在发生第一个事件时生成 INT

EPwm7Regs.ETCLR.ALL = 0x000F;//清除所有 ETFLAG