主题中讨论的其他器件:SFRA

您好!

闭环 PCMC 的默认补偿为 Z0 = 0.0001kHz、Z1 = 25kHz 和 P1 = 3kHz。 我认为电流模式只需要1极点和1零即可进行补偿。 而 DCL22意味着两个极点和两个零。 您能否解释一下默认情况下使用的零点和极点值。 Z0值在这里意味着什么? 它太低。 在极点之后、Z1和 P1的值也似乎是奇数的。

此外、在 VMC 中、我只能在代码中看到两个零极和一个极点。 第二个极点放置在何处?

谢谢、

Ajit

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

闭环 PCMC 的默认补偿为 Z0 = 0.0001kHz、Z1 = 25kHz 和 P1 = 3kHz。 我认为电流模式只需要1极点和1零即可进行补偿。 而 DCL22意味着两个极点和两个零。 您能否解释一下默认情况下使用的零点和极点值。 Z0值在这里意味着什么? 它太低。 在极点之后、Z1和 P1的值也似乎是奇数的。

此外、在 VMC 中、我只能在代码中看到两个零极和一个极点。 第二个极点放置在何处?

谢谢、

Ajit

Ajit、

DF22的第一个极点根据设计固定为0Hz。 您可以在补偿设计器 GUI 中看到此推理、其中 fp0 显示 为0、无法修改。 如果您更喜欢用这些术语来思考、DCL 用户指南还显示了基本的行为方程。

PID 是 PCMC 的突出显示补偿负载模型。 为了获得安全的工作点、通过与补偿设计器进行经验迭代而不是通过数学推导来实现最佳放置、可以找到一组可接受的默认 ZPK 加载值。

实际上、我认为 Z1=25kHz 的影响最小、因为 它超出系统带宽。 Z0=0.1Hz 实际上为零、有助于在0Hz 时消除 P0。 因此、这会将 P1=3kHz 作为主调谐器。

Tommy

嗨、Tommy、

感谢您的澄清。 请您帮助我解决以下疑问。

在 Plant Bode 图中、Plant Bode 图为什么具有0dB 直流增益。 它实际上应该是 VIN (9V)的幅度、这意味着大约19dB。

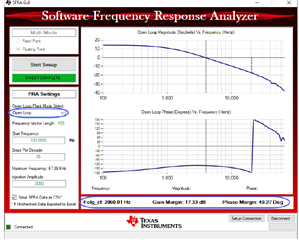

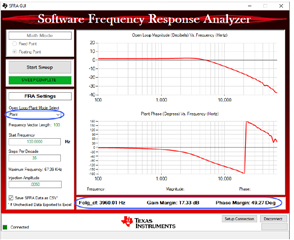

在开环 VMC 情况下、受控体和开环实际上应该是相同的东西? 为什么这里的波特图不同(见下文)

此外、由于 LC 明显与此处的情况不同、该设备应具有双极。 如果 ESR 零点接近极点、则相位滞后不应为180度、这种情况也不是如此。 也请说明这一点

我还建议查看 SFRA 文档、了解如何实施该文档的详细信息。

[引用 userid="283871" URL="~/support/microcontrollers/c2000/f/c2000-microcontrollers-forum/991329/boostxl-buckconv-compensation-for-closed-loop-pcmc-and-vmc-default-location-of-poles-and-zeros/3665535 #3665536]在 Plant 波特图中、Plant 波特图为什么具有0dB 直流增益。 它实际上应该是 VIN (9V)的幅度、这意味着大约19dB。[/引述]SFRA 输入和图形被抽象化为标幺值。 需要根据控制和反馈增益计算控制和 Vout 电平的绝对幅度。

[引用 userid="283871" URL"~/support/microcontrollers/c2000/f/c2000-microcontrollers-forum/991329/boostxl-buckconv-compensation-for-closed-loop-pcmc-and-vmc-default-location-of-poles-and-zeros/3665535 #3665536"]在开环 VMC 情况下、受控体和开环实际上应该是相同的东西? 为什么这里的波特图不同(见下文)

此外、由于 LC 明显与此处的情况不同、该设备应具有双极。 如果 ESR 零点接近极点、则相位滞后不应为180度、这种情况也不是如此。 也请说明这一点

[/报价]我会要求一些同事提供意见。