使用的芯片型号:(使用的芯片型号:)

2、用途(目的):

想要给这个芯片外接一个SDRAM的存储器。μ A

3、问题(存在的问题):

(__LW_AT__1 μ)DSP的GPIO 72引脚被Boot 模式选择 Switch占用了

此时外扩的SDRAM的数据位D12也是需要接到GPIO72上的。μ A

DSP 的 GPIO_72引脚被引导模式选择开关占用。

此时、扩展 SDRAM 的数据位 D12也需要连接到 GPIO72。

(__LW_AT__)DSP的GPIO μ 44引脚被ethernet的引脚占用了 μ A

此时外扩的SDRAM的地址位A4也是需要接到GPIO44上的。μ A

DSP 的 GPIO_44引脚被以太网的引脚占用。

此时、扩展 SDRAM 的地址位 A4也需要连接到 GPIO44。

(__LW_AT__3 μ)DSP的GPIO μ 75引脚被ethernet的引脚占用了

此时外扩的SDRAM的数据位D9也是需要接到GPIO75上的。μ A

DSP 的 GPIO_75引脚被以太网的引脚占用。

此时、扩展 SDRAM 的数据位 D9也需要连接到 GPIO75。

4、尝试解决方案(尝试解决方法):

尝试1:(只修改冲突的地址线和数据线)μ A

将外扩的SDRAM冲突的地址线A4连接到EMIF1 ć A13上(不按照原来的SDRAM ć A4连接到EMIF1 ć_A4)ć

将外扩的SDRAM冲突的数据线D9、D12对应连接到EMIF1的D16和D17上(不按照原来的SDRAM ć_d9、D12连接到EMIF1 ć_d9、)ć

尝试1:(仅修改冲突的地址行和数据行)

将外部扩展的 SDRAM 冲突地址行 A4连接到 EMIF1_A13 (根据原始 SDRAM_A4、不连接到 EMIF1_A4)。

将外部扩展 SDRAM 的冲突数据线路 D9和 D12连接到 EMIF1的 D16和 D17 (根据原始 SDRAM_D9和 D12、未连接到 EMIF1_D9和 D12)。

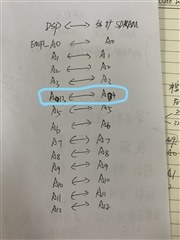

连接方式如下图:μ A

连接方法如下:

尝试2:(将SDRAM的地址线和数据线整体平移连接到DSP的EMIF1上)μ A

将外扩的SDRAM的地址线A0 μ A12连接到EMIF1 μ A17上 A5 μ A

将外扩的SDRAM的数据线D0 - D15连接到EMIF1 _D16 - D31上

尝试2:(将 SDRAM 的地址线和数据线连接到整个 DSP 的 EMIF1进行转换)

将外部扩展 SDRAM 的地址行 A0-A12连接到 EMIF1_A5-A17

将外部扩展 SDRAM 的数据线路 D0-D15连接到 EMIF1_D16-D31

5、要询问的问题(请教的问题)

上述两种尝试的连接方式,如果选择第一种尝试方式,(只修改冲突的地址线和数据线),不修改其他的地址线和数据线。μ A

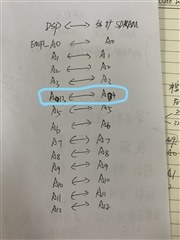

如下图的这种连接方式:μ A

如果您为上述两次尝试选择第一种连接方法(仅修改冲突的地址行和数据行)、请勿修改其他地址行和数据行。

此连接方法如下图所示:

这种连接方式,地址线和数据线不是对应连接的,在CCS端进行程序驱动的时候,也是方便的吧,只需要硬件上连接之后,代码里面修改一下引脚,如下图所示,修改成注释的样子:μ A

在这种连接方法中、地址线和数据线没有相应地连接。 在 CCS 端驱动程序时也很方便。 只需在连接硬件后修改代码中的引脚、如下图所示。 注释如下所示:

按照这样修改,是否符合DSP的外扩连接的标准?是否影响SDRAM的正常使用呢?μ A

根据此修改、它是否符合 DSP 的外部扩展连接标准? 它是否影响 SDRAM 的正常使用?

6、 选择尝试1的原因是(选用尝试1的原因是):

方便PCB图的修改。μ A

修改 PCB 图非常方便。

7、您对修改的建议是什么?(请教一下,您的修改建议是?)

我在这里要问!

谢谢!

特来请教!μ A

感谢!μ A