您好!

我计划使用 CMPSS 的迟滞功能。 我看到一个名为 COMPHYSCTL 的寄存器。 我将 ADCINB6连接到高比较器的正输入端、将 DAC 基准连接到高比较器的负输入端。 现在、我需要设置迟滞 并确定两个阈值电平。 请就此提供帮助。

COMPHYSCTL 的解释如下。

"

比较器迟滞。 设置上的迟滞量

比较器输入。

0无

1设置为典型迟滞

2设置为典型迟滞的2倍

3设置为典型迟滞的3倍

4设置为典型迟滞的4倍

"

还有其他信息、如下所示。

但我无法理解上述内容、而且信息存在冲突。 什么是"典型迟滞的4倍"? 什么迟滞?

1) 1)这意味着"典型磁滞的4倍"? 什么是典型迟滞? 哪个值乘以4? 请提供公式、以便让我完全理解。

2) 2)向 COMPHYSCTL 写入4 足以设置迟滞?

3) 3)上表(1)中的解释含义是什么? 它说 CMPSS DAC 用作基准。 不过、我将 COMPHYSCTL 置1 来控制迟滞? COMPHYSCTL 和 CMPS DAC 基准之间有何关系? 它们是如何缩放迟滞的? 哪一个驱动真正的迟滞?

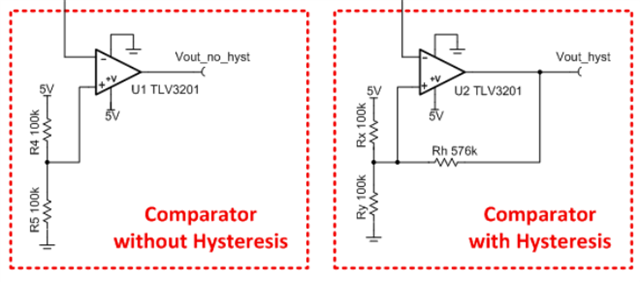

4) 4)我插入到具有迟滞的实际模拟比较器下方。 比较器的正输入和输出之间存在连接。 它提供了迟滞。 但是、我无法为 MCU 内部设置关系。 我只将 ADC 输入连接到 CMPSS 输入。

5) 5)如何确定高阈值和低阈值?

提前感谢您。