主题中讨论的其他器件:BOOSTXL-DRV8320RS、 INA240、 EK-TM4C1294XL、 MOTORWARE、 TMS320F280049C

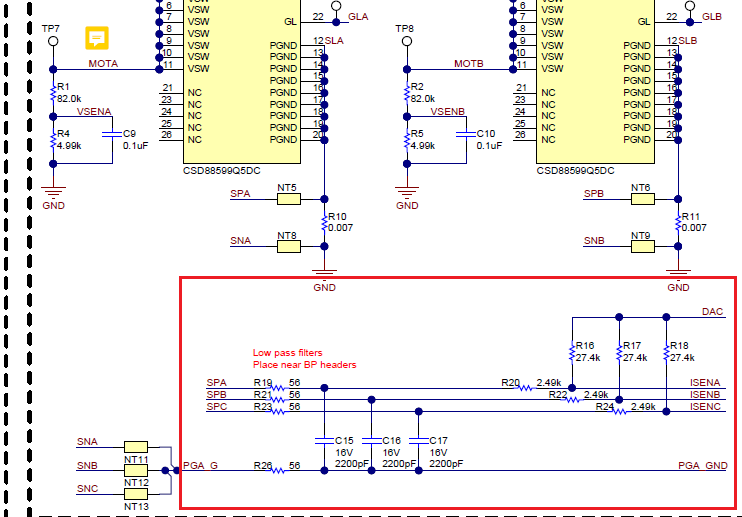

请参阅以下 TI 文档图、其中涉及外部电流监控器与使用内部 PGA。

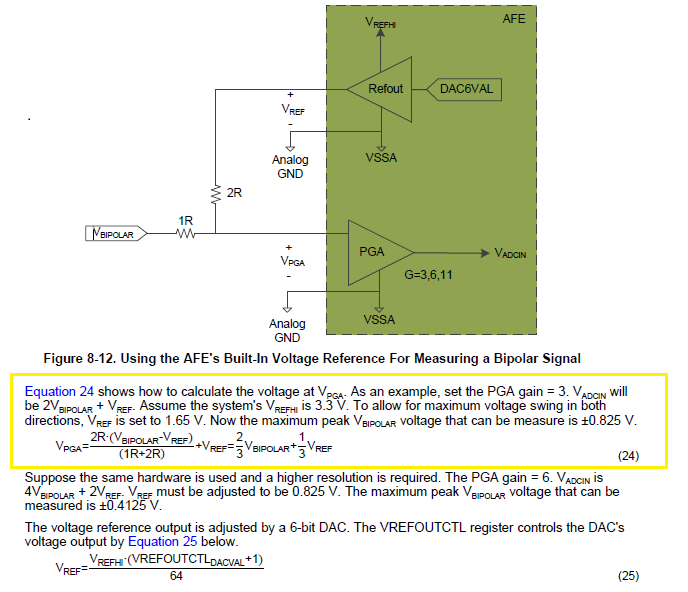

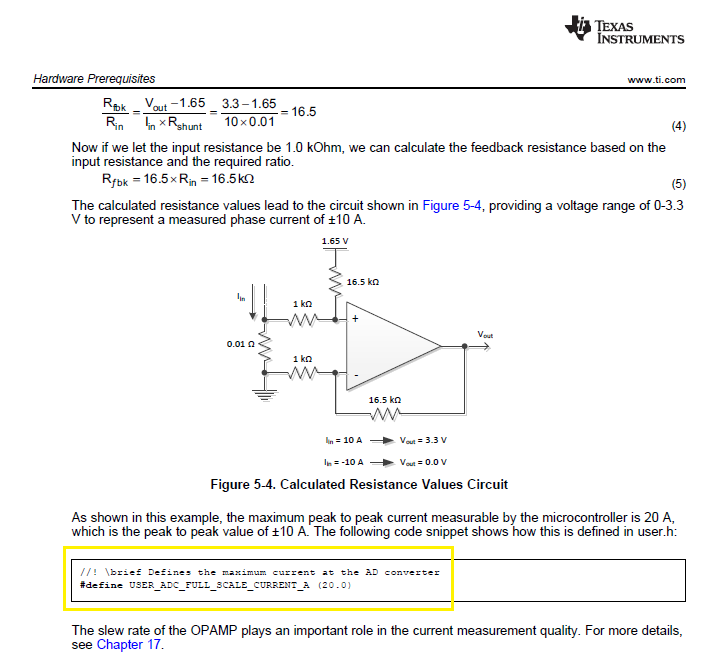

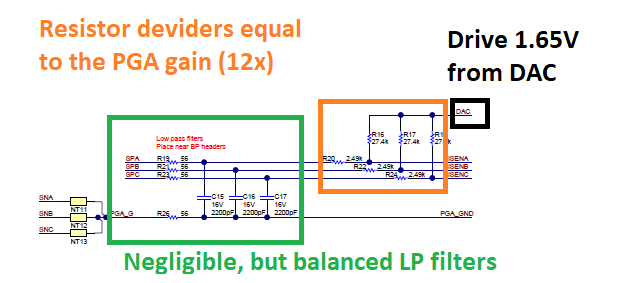

使用8.6.2.3第356-357页中的示例 SPRUHJ1H–2013年1月–2019年6月修订版中的图8-12和第230页中的图5-4:

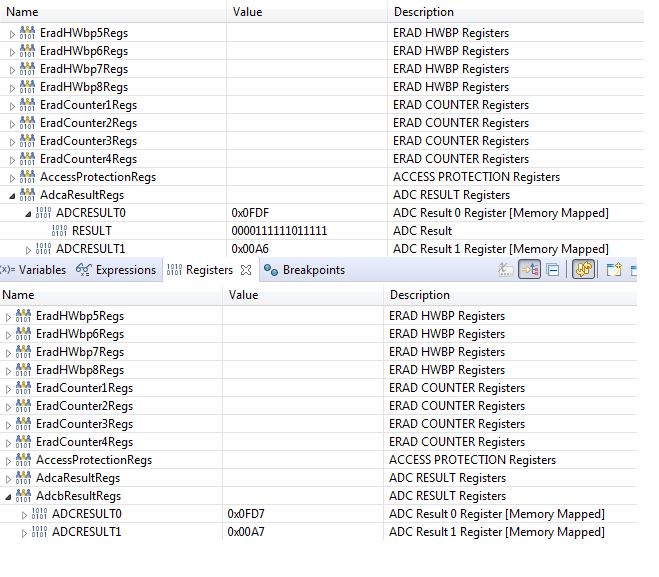

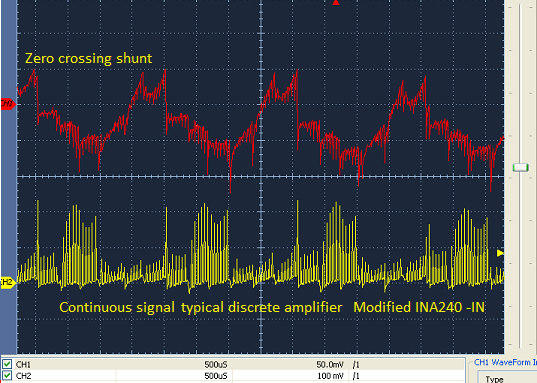

A1: PGA 输出模拟信号似乎过零(移除了 R19、R22、R25)、J5引脚45、46、 48已断开连接。

A2:为 R26选择0r、R27 PGA_GND、因为(对于 x3增益、Rgnd=10k)图 8-12.

请详细说明 A2如何根据显示 x3增益的公式(黄色框)将 PGA 输出设置为中心1.65v?

公式(黄色框)图 8-12显示2*VBIPOLAR (+/-0.820mv)+ Vref (1.65v)= Adcin (3V3)。

2.为什么需要输入滤波器(以下)的 PGA 设置 x12增益来为用户 ADC 比例因子(user.h)生成正确的结果?

3. PGA 输出(Vadcin)中心是否为(1.65v)(如公式所示)、PGA 增益设置为 x3?

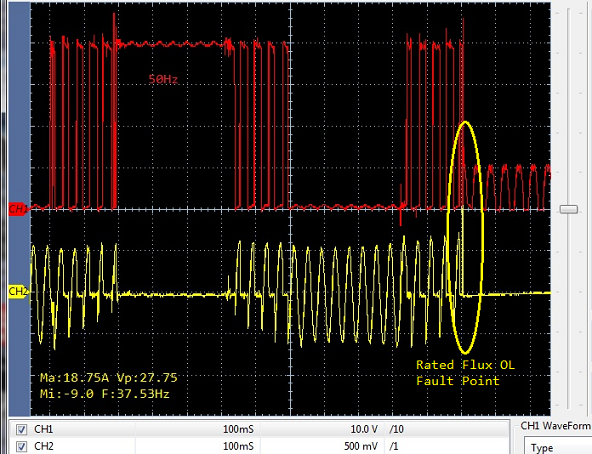

这一点对于 CMPSS 和 DAC 滤波器跳闸行为而言似乎很重要。

14.10模拟前端集成

PGA 与其他嵌入式模拟模块(ADC、CMPSS、缓冲 DAC)配合工作、用作模拟前端系统。

并将外部 DACA J7引脚70用于 Vref;每当 ePWM TripIN 区域出现时、DAC Vref 电平将更改为1.65、设置为1.35V。

/*将 DACA 输出设置为1.35V 中心、INA240 Ref1/2 */ DAC_setShadowImage Value (obj->dacHandle[1]、1646U);/2048

4、如果 PGA 以1.65v 为中心、为什么 PGA 似乎从未触发 CCMPSS DAC 滤波器故障采样阈值?

然而、外部中心(1.65V)电流监控器可轻松应用于模拟子系统(TRM:图12-4) GX_ADCAB、GxADCC。

5. TI 是否曾使用 LauchXLx-49C 对外部电流监控器进行过测试、以验证 DAC 滤波器和换算系数公式是否按预期工作?