尊敬的先生:

我们正在使用双 C2000 CPU (TMS320F2837x)开发一个 SIL-3器件。

每个 CPU 都有自己的 RAM 和时钟。 代码也存储在其存储中。 我们已使用诊断库对各个 CPU 进行自检。

由于使用两个 CPU、每个 CPU 将从其存储中执行其代码。 对于安全功能、顾问要求我们比较双 CPU 代码执行的结果。

我们已经看到一个使用 spear 1300 CPU 的参考设计。

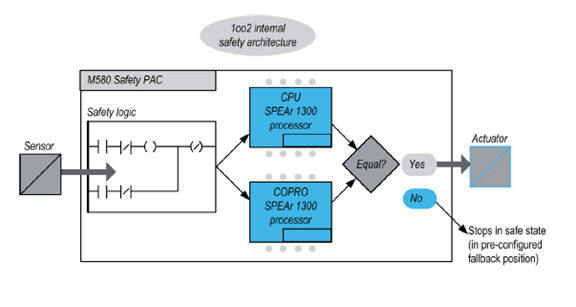

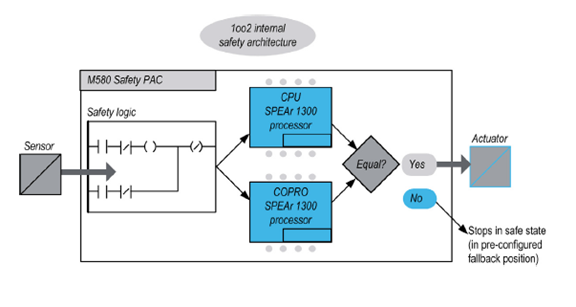

Schneider M580提供以下 SIL3安全级别功能

安全任务代码的独立双执行。

2.双代码执行结果的比较。

3.定期自检。

4.支持1oo2 (“两个中的一个”)体系结构。

如何比较两个 CPU 之间的结果? 是否有参考样片? 软件还是硬件?

此致、

Eddie