C2000团队、

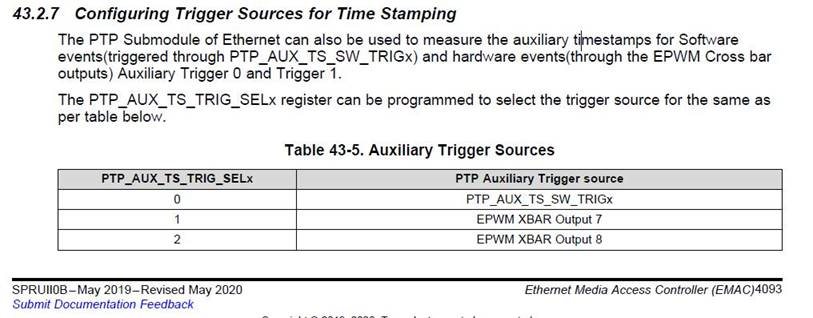

在 F28388D 上、客户正在使用 Cortex-M 中以太网的 AUX_Timestamp 功能 它们使用 ePWM XBAR 输出8来触发此情况。

ePWM XBAR 输出8由 INPUTXBAR4提供、而 INPUTXBAR4又由 GPIO95提供。 GPIO95又从 CLB 输出馈送。 是的、布线非常重! 其配置代码为:

Xbar_setCLBOutputMuxConfig (CLBOUTPUTXBAR_base、XBAR_OUTPUT5、XBAR_OUT_MUX06_CMPSS4_CTRIPOUTH_OR_L);

Xbar_enableCLBOutputMux (CLBOUTPUTXBAR_BASE、XBAR_OUTPUT5、XBAR_MUX06);

GPIO_setPadConfig (95、GPIO_PIN_TYPE_STD); // GPIO95是引脚

GPIO_setDirectionMode (95、GPIO_DIR_MODE_OUT);

GPIO_setPinConfig (GPIO_95_CLBOUTPUTXBAR5);

Xbar_setInputPin (INPUTXBAR_base、XBAR_INPUT4、95);//将 GPIO95设置为输入 XBar4以实现组合跳闸输入

Xbar_setEPWMMuxConfig (XBAR_TRIP8、XBAR_EPWM_MUX07_INPUTXBAR4);// GPIO95连接到 INPUTXBAR4,将该信号传递到 ePWM XBAR 输出8 */

Xbar_enableEPWMMUX (XBAR_TRIP8、XBAR_MUX07); //此信号将用于在 CM 上触发 PTP 时间戳*/

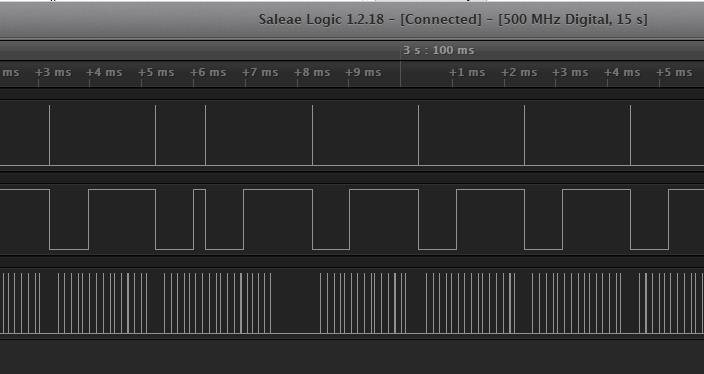

除了时间戳是在 GPIO95的下降沿触发之外、其他操作看起来都是这样的。 以下是逻辑分析仪屏幕截图:

顶部走线是辅助时间戳、中间走线是 GPIO95。

问题:我们需要使用时间戳来触发 GPIO95的上升沿(同样、也是 ePWM XBAR 输出8)。 假设时间戳始终在触发信号的下降沿触发、我们需要对信号进行反相以生成正确的时序。

我们尝试过的内容:

1)反相跳变极性: EPwmXbarRegs.TRIPOUTINV.bit.TRIP8 = 1;

2) 2)使用 GPyINV 寄存器在 GPIO 输入端反相 GPIO95。

3) 3)反转 CLB 中的信号(在路由到 GPIO95之前)。

上述任何一项似乎都没有任何效果。

我们已检查 EALLOW 问题、并使用 CCS 确认寄存器已按预期配置。

我们知道时间戳是从 GPIO95触发的、因为如果我们将 INPUTXBAR4选择更改为0、而不是95、则没有 cortex-M 时间戳(这意味着没有触发信号)。