主题中讨论的其他器件:TMS320F28377S、 C2000WARE

我们正在处理一个奇怪的问题、在 C2000ware 中使用 F2837xS_SYSCTRL.c 中的 InitSysPll 函 数的细微修改版本时会发现这个问题。 我已经查看了 C2000ware 的最新版本(v3.02.00.00)、以确认我们与最新版本保持一致。 下面引用的所有行号都将与该代码对应。 此测试是在使用10MHz 外部时钟源的 TMS320F28377S LaunchPadXL 上进行的。

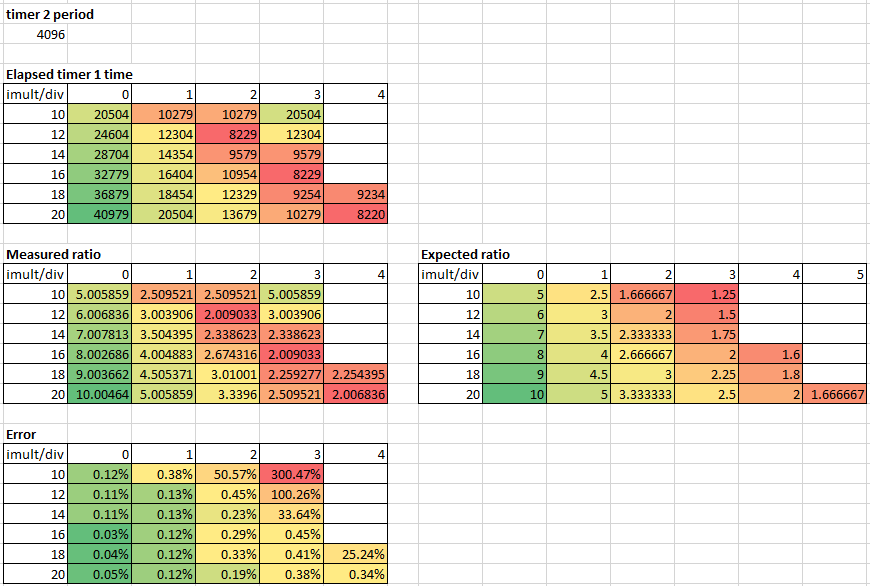

我们发现、函数的某些输入组合会导致第1004行的 sysclkInvalidFreq 为 true。 总是当第999行上的 mult/div 值小于2.0时。 这无法通过查看表5-12内部时钟频率中提供的数据表(SPRS881H)中的有效频率范围来解释。

我们可以通过以下设置获取 sysclkInvalidFreq 来评估 false:

| 时钟源 | 结果 | fmult | 迪索尔 |

| XTAL_OSC | 12. | 0 | 2. |

| XTAL_OSC | 14. | 0 | 2. |

| XTAL_OSC | 16. | 0 | 3. |

| XTAL_OSC | 18 | 0 | 3. |

| XTAL_OSC | 20. | 0 | 4. |

但是、当我们针对每种情况将 divsel 增加1时、mult/div 的值会降至2以下、sysclkInvalidFreq 会计算为 true。

我们希望在此提供任何帮助、以便我们能够了解这种行为的原因。 谢谢!