您好!

我们使用 TMS320F28069的 ePWM 输出来控制半桥。

初始化后、仅调整 PWM 机器的比较值。

这发生在 CLA 中断中。 PWM 机器以30kHz 的频率在上行关闭模式下运行。

Epwm1A 和 Epwm1B 用于上 IGBT 和下 IGBT 同步和反相。

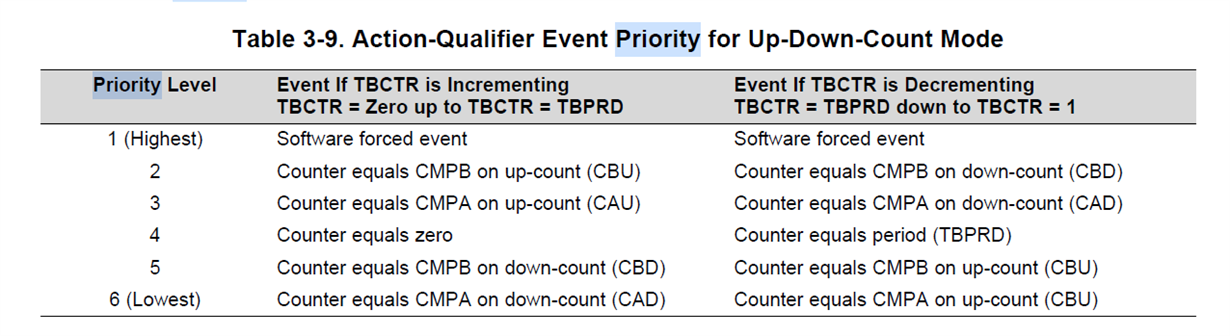

我们希望更改 CTR =零和 CTR =周期时的占空比。 CMPA 应用于两个 PWM。

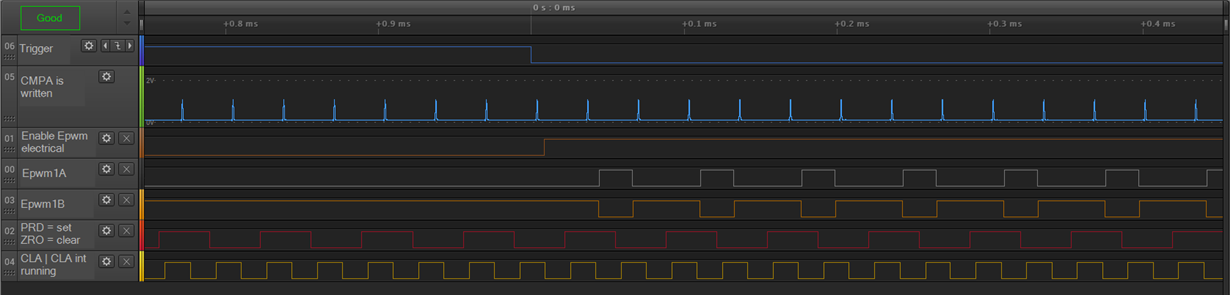

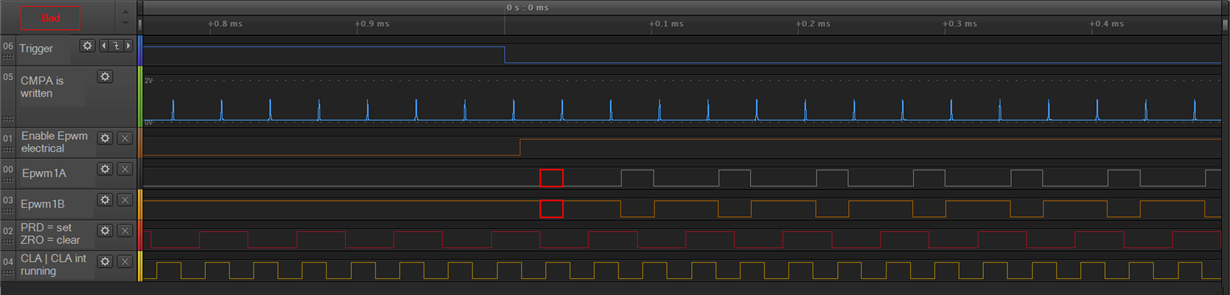

在我的测试中、我注意到在比较值有效之前、输入 CLA_int 的2到3倍。

我的预期是、在 CLA_int 中计算得出的 CompareValue 将从下一个 CTR =零或 CTR =周期事件生效。

这种延迟来自哪里?

Epwm1的初始化如下:

EPwm1Regs.TBPRD = PWM_PERIode _已使用;//90e6/30e3

EPwm1Regs.TBPHS.Half.TBPHS = 0;

EPwm1Regs.TBCTL.bit.CLKDIV = TB_CLKDIV_DIV1;//0

EPwm1Regs.TBCTL.bit.HSPCLKDIV = TB_HSPCLKDIV_DIV1;//0

EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO;//1.

EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW;//0

EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE;//0

EPwm1Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN;//2.

EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADODE;//0

EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;//0

EPwm1Regs.CMPCTL.bit.LOADAMODE = CC_CTR_Zero_PRD;//2.

EPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_Zero_PRD; //2.

EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR;//1.

EPwm1Regs.AQCTLA.bit.CAD = AQ_SET;//2.

EPwm1Regs.AQCTLB.bit.CAU = AQ_SET;//2 -可能不需要

EPwm1Regs.AQCTLB.bit.CAD = AQ_CLEAR;//1-可能不需要

EPwm1Regs.DBCTL.bit.HALFCYCLE = 0;

EPwm1Regs.DBCTL.bit.IN_MODE = DBA_ALL;//0

EPwm1Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;//2.

EPwm1Regs.DBCTL.bit.OUT_MODE = DB_FUL_ENABLE;//3.

EPwm1Regs.DBRED = 42;

EPwm1Regs.DBFED = 42;

EPwm1Regs.TBCTL.bit.FREE_SOFT = 0;

此致、

Dominik