您好!

我有几个客户提出的问题、他们现在正在设计自己的电路板。

Q1) VDD 去耦电容:

根据数据表、

“μF 建议在每个 VDD 引脚附近放置一个总电容约为22 μ F 的去耦电容器。”

客户希望确保每个 VDD 引脚需要连接在一起或不连接在一起。

如果不是、应如何为每个 VDD 引脚分配22uF 电容?

示例 假设有48个 QFP、则有两个 VDD 引脚。 一个引脚2uF、另一个引脚20uF 是可以接受的?

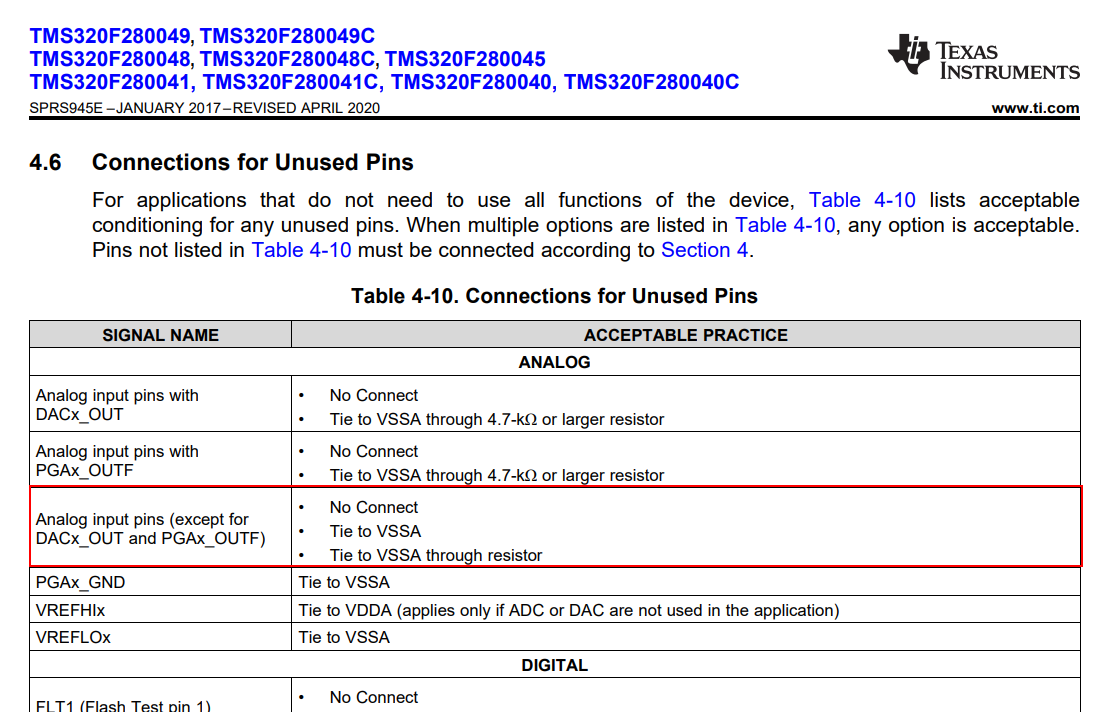

Q2)未使用的 AIO 引脚:

不清楚如何处理未使用的 AIO 引脚。 它们未列在数据表表表表4-9中。

这是否可以连接 VSS?

Q3) VREFHI 引脚用法:

如果使用内部基准、添加2.2uF 电容器就足够了、对吧?

谢谢、此致、

田志郎一郎