主题中讨论的其他器件: C2000WARE

工具/软件:Code Composer Studio

您好!

我有一个与 DSP TMS320F28377S 的 ePWM 输出相关的问题。

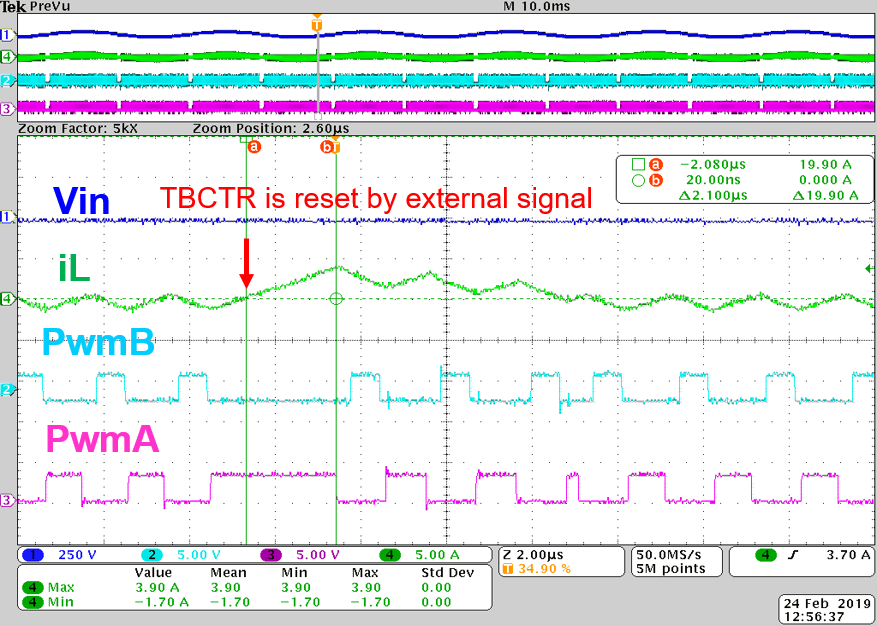

在我的代码中、EPWM7输出根据感应信号和一个中断中占空比的实时计算进行更新。 如下图所示、PWM 输出有时在一个开关周期内全部在 A 中为高电平、在 B 中全部为低电平、看起来像是毛刺脉冲或错误。 我在 PWM 生成中使用了互补模式。 此类干扰以非常低的频率发生(有时捕获一个干扰需要10秒)。 感应到的外部信号和实时计算都应该正确。 由于我的采样频率为50kHz、开关频率平均为300kHz、如果计算和感应信号出现问题、PWM 干扰将持续几个开关周期、而不是仅一个周期、并在如此低的频率下发生。 因此、它在更新占空比时看起来更像是 PWM 干扰。

我想知道、什么会导致像这样的 ePWM 模块干扰或错误? 如何避免这种现象?

顺便说一下、PWM 的初始化函数如下所示。 ePWM_TIMER_TBPRD、ePWM_CMPA、ePWM_CMPB、ePWM_TIMER_PHASE、RED 和 FED 的值根据一个 ADC 中断中的计算结果进行更新。

//代码//////////////////////////

空 InitEPwm7()

{

//设置 TBCLK

EPwm7Regs.TBCTL.bit.CTRMODE = TB_COUNT_UP;//向上计数

EPwm7Regs.TBPRD = ePWM_TIMER_TBPRD;//设置定时器周期

EPwm7Regs.TBCTL.bit.PHSEN = TB_ENABLE;//启用相位加载

EPwm7Regs.TBPHS.bit.TBPHS =0x0000;//相位为0

EPwm7Regs.TBCTL.bit.PRDLD = TB_SHADOW;//

EPwm7Regs.TBCTL2.bit.SYNCOSELx=1;//同步输出的扩展选择、EPWMxSYNCO = CMPC

EPwm7Regs.TBCTL.bit.SYNCOSEL = 3;//0:同步输出选择为 SYNC 信号;1:当 TB 计数器= 0时;3:扩展、

EPwm7Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1;//时钟与 SYSCLKOUT 的比率

EPwm7Regs.TBCTL.bit.CLKDIV = TB_DIV1;

//

//将影子寄存器加载设置为零

EPwm7Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm7Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm7Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm7Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

EPwm7Regs.CMPCTL2.bit.SHDWCMODE = CC_SHADOW;

EPwm7Regs.CMPCTL2.bit.LOADCMODE = CC_CTR_ZERO;

//

//设置比较值

EPwm7Regs.CMPA.bit.CMPA = ePWM_CMPA;//设置比较值

EPwm7Regs.CMPB.bit.CMPB = ePWM_CMPB;//设置比较 B 值

EPwm7Regs.CMPC = ePWM_TIMER_PHASE;// 0.5 TS

//

//设置 outputA 上的操作,EPWM7A 是 SR 开关的原始 PWM

EPwm7Regs.AQCTLA.bit.CAU = AQ_SET;//在事件 A 上设置 PWM1A、递增计数

EPwm7Regs.AQCTLA.bit.CBU = AQ_CLEAR;//在事件 B 上清除 PWM1A、递增计数

//

//设置死区发生器

EPwm7Regs.DBCTL.bit.IN_MODE = DBA_ALL;//EPWMA 是下降沿和上升沿的源

EPwm7Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE;//启用死区模块、波特图和红色有效

EPwm7Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC;//高电平有效互补

EPwm7Regs.DBRED.bit.DBRED =红色;//在打开 SR 开关之前设置死区时间

EPwm7Regs.DBFED.bit.DBFED= FED;//在打开交流开关之前设置死区时间、TR

//通过跳闸1的 Vo 过压时关闭栅极信号

EALLOW;

EPwm7Regs.TZSEL.bit.OSHT1 = 1;//启用 T1作为触发信号

EPwm7Regs.TZCTL.bit.TZA = 2;//强制 EPWM7A 为低电平

EPwm7Regs.TZCTL.bit.TSB = 2;//强制 EPWM7B 为低电平

EDIS;

//在过流通过跳闸2时关闭栅极信号

EALLOW;

EPwm7Regs.TZSEL.bit.OSHT2 = 1;//启用 T2作为触发信号

EPwm7Regs.TZCTL.bit.TZA = 2;//强制 EPWM7A 为低电平

EPwm7Regs.TZCTL.bit.TSB = 2;//强制 EPWM7B 为低电平

EDIS;

//过流通过跳闸3时关闭栅极信号

EALLOW;

EPwm7Regs.TZSEL.bit.OSHT3 = 1;//启用 T3作为触发信号

EPwm7Regs.TZCTL.bit.TZA = 2;//强制 EPWM7A 为低电平

EPwm7Regs.TZCTL.bit.TSB = 2;//强制 EPWM7B 为低电平

EDIS;

}

如果您能给我任何提示或建议、我将不胜感激。 这个问题对于我的整个实验来说非常重要。

期待您的回复。