主题中讨论的其他器件:AMC1303E2510、 AMC1306M25

您好!

我正在使用 TMS320F28075 SDFM1的 Filters1、2和3来读取来自3 个单独的 AMC1303E2510芯片的曼彻斯特编码输出。 AMC1303E2510 具有其内部生成的10MHz CLK、因此我使用 CMPC 和 ePWM11的 CMPD 来同步 SDFM1的滤波器1、2和3。 在读取每个滤波器的结果后、它被重新缩放到 DAC 范围(0-4095)、3个滤波器输出在3个 DAC 上输出。 我已经附加了下面项目的主.c 文件。

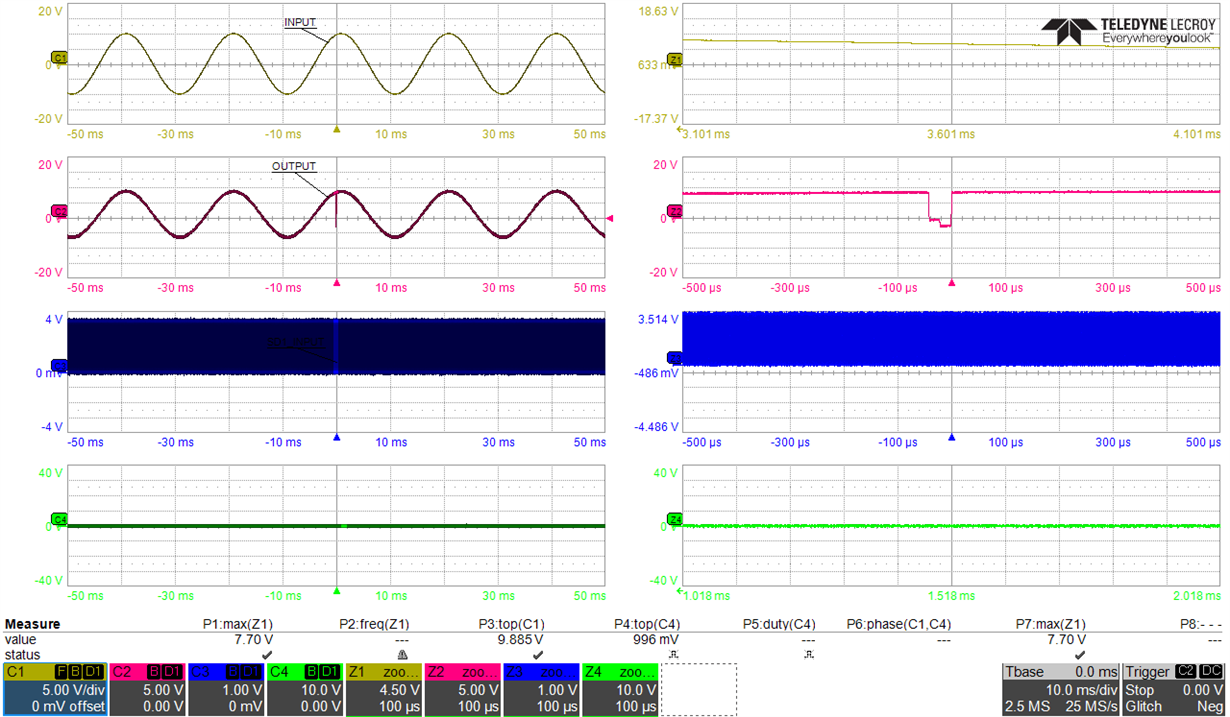

我遇到的问题是 SDFM 模块的输出有时是错误的。 在下面的示波器快照中:

- CH1 (黄色)是滤波器1 AMC1303芯片的+/-10V 输入(通过电阻分压器)。 +/-10V 在 AMC1303输入端产生+/-250mV 电压。

- CH2 (粉色)是滤波器1的 DAC 输出(请注意、它通过外部运算放大器缓冲器来增加其振幅)。

您可以在 CH2的放大图中看到、DAC 输出在大约40uS 内是错误的(在代码中、SDFM 采样周期大约为20us、因此这对应于 SDFM 模块中的2个错误值)。 我还验证了问题与 DAC 转换无关(即从 SDDATA 寄存器中读取的滤波器1的原始数据不正确)。

当 ePWM1计数器为0时、ISR 例程 epwm1_ISR 被触发。 它配置为向上计数模式。 PWM 周期被设定为 SDFM 采样周期的4倍。 这是因为在 PWM 同步之后、前两个 SDFM 输出值不正确(使用 SINC3滤波器)。 ePWM11的设置与 ePWM1相同、并通过由 ePWM10馈送的来自 ePWM1的同步脉冲输入与 ePWM1计数器同步。

ePWM11.CMPC 和 CMPD 被设定为 SDFM_RESET_CMP_VALUE。 设置 SDFM_RESET_CMP_VALUE、以便在 PWM 计数器重置为0之前发生数据滤波器延迟+ 5个 SD 时钟周期。 因此、在 CMPC/CMPD PWM 同步之后、在 ISR 触发之前、应该有3个 SDFM 输出值的时间。 因此、我确信问题不是因为我在 PWMSYNC 事件之后读取了2个不正确的样本中的一个。

在 ISR 中、检查滤波器1、2和3的 ACK 和调制器故障标志。 如果任何 ACK 标志未设置或调制器故障标志已设置、则例程暂停(使用 ESTOP0)。 但是、即使值不正确、也不会发生这种情况。

最后、我在数据表和其他线程中看到、Δ-Σ 芯片(在本例中为 AMC1303E2510) CLK 周期必须介于8*T_SYSCLK - 20*T_SYSCLK 之间。 在我的代码中、我使用的是该行

InitSysPll (INT_OSC2、IMULT_10、FULT_0、PLLCLK_By_1);

将 MCU CLK 频率设置为100MHz。 因此 T_SYSCLK = 10ns。 因此 Δ-Σ CLK 周期必须介于80ns - 200ns 之间。 对于10MHz Δ-Σ CLK、周期为100ns、因此该值应该很小。

您看到我所描述的设置有什么问题吗? 您以前是否见过这种行为?

非常感谢、

费尔加尔

e2e.ti.com/.../8322.sdfm_5F00_pwm_5F00_sync_5F00_cpu_5F00_cpu01.c