器件型号:TMS320F28035

a:许多 C2000器件具有内部电路来检测是否发生了看门狗复位(WDRST)或上电复位(POR)/外部复位(通过激活-XRS 引脚)。 本文介绍了此电路的工作原理以及在系统中使用 WDFLAG 时对–XRS 引脚的系统要求。 本文适用于2823x/2833x/2802x/2803x/2805x/2806x 器件。 有关此机制在不同器件型号上的工作方式可能存在的任何差异、请参阅相应器件的数据表和技术参考手册(TRM)。

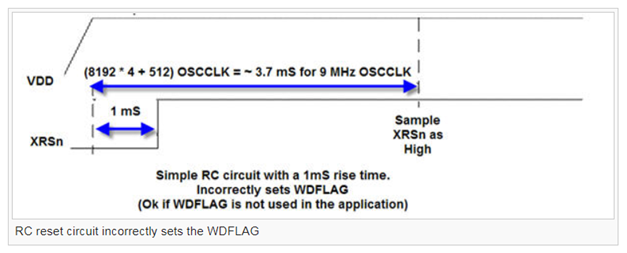

本页上的计算假设 OSCCLK≈9MHz。

WDFLAG 行为

看门狗模块中的 WDFLAG 位用于使系统能够区分看门狗复位(WDRST)或上电复位(POR)/外部复位。 器件内的电路在一个延迟后对-XRS 线路进行采样、以区分看门狗复位(WDRST)和一个 POR/外部复位。

当-XRS 线路被拉低时、WDFLAG 位被强制为低电平。 仅当-XRS 引脚在延迟8192 * 4 + 512个 OSCLK 周期后被采样为高电平时、才会设置 WDFLAG 位。 如果此时-XRS 引脚被采样为低电平、WDFLAG 位将保持为0。 因此、为了区分看门狗复位和外部器件复位、外部复位的持续时间必须长于该采样时间。

注意:复位时、OSCCLK 是 SYSCLKOUT 的四倍。 8192个 SYSCLKOUT 周期转换为8192 * 4个 OSCCCLK 周期。 这是延迟公式中4倍乘的来源、因为延迟是用 OSCCLK 表示的。 WDRST 为512 OSCCLKS、因此延迟被添加到此值。

下面总结了 WDFLAG 位对每种复位类型的行为方式:

加电后的 POR 或外部复位

在这种情况下,需要将 WDFLAG 位设置为“0”,以指示复位不是由 WDRST 引起的。 为了实现这一点、XRS 必须保持低电平的时间必须长于(8192 * 4 + 512) OSCCLK 周期。 此时、将对-XRS 线路进行采样、如果该线路为低电平、则 WDFLAG 将保持为0。 对于 INTOSC = 10MHz 的器件、对于9MHz OSCCLK、时间为~3.7ms。

注意:OSCCLK 频率使用的下限值为9MHz、而不是10MHz。 这是为了在校准前考虑振荡器频率偏差。

如果-XRS 引脚在采样时不是低电平、则 WDFLAG 位将被置位、这将错误地指示看门狗已触发复位。

看门狗启动复位(WDRST)时

在本例中,我们希望 WDFLAG 位为“1”。 当一个 WD 计数器溢出时、内部 WD 复位信号(WDRST)将把-XRS 线路拉低(仅) 512个 OSCCLK 周期。 当 WDRST 释放线路时、–XRS 引脚将在由–XRS 引脚上的电容确定的一段时间后返回高电平状态。 此设计必须确保–XRS 引脚在8192 * 4 + 512 OSCLK 周期之前变为高电平、此时–XRS 引脚将被采样。 如果它被采样为高电平、WDFLAG 将被置位。 请注意、WDFLAG 仅在 WDRST 失效(变为高电平)之后(8192 * 4)个 OSCLK 周期后置1。 由于 WDRST 为512个 OSCLK 周期宽、因此在 WDRST 开始后(当它变为低电平时)、WDFLAG 标志将被设定~3.7ms。

XRS 引脚的连接

根据应用需求、XRS 引脚可能需要在不同设计中采用不同的处理方式。

情况1:不需要区分 WDRST 和 POR/外部复位:

如果看门狗复位和 POR /外部复位之间的区别不是一个问题、那么-XRS 引脚上的上拉电阻器(出于抗噪的原因)就足够了。 一些 controlCARD 具有简单的上拉电阻、属于这种情况。 下图显示了在 OSCCLK≈9MHz 时使用简单 RC 电路会导致 WDFLAG 被错误设置的原因。

情况2:需要区分 WDRST 和 POR/外部复位:

如果需要区分看门狗复位和 POR /外部复位、则需要考虑其他设计注意事项。

器件中有一个延迟 XRS 线路采样的电路、用于区分看门狗复位(WDRST)和正常复位。 为了区分看门狗复位和外部器件复位、外部复位的持续时间必须长于看门狗脉冲(512个 OSCCLK 周期)+ 8192个 SYSCLKOUT 周期延迟。

复位时、SYSCLKOUT=OSCCLK/4。 因此、外部复位脉冲需要长于3.7ms。

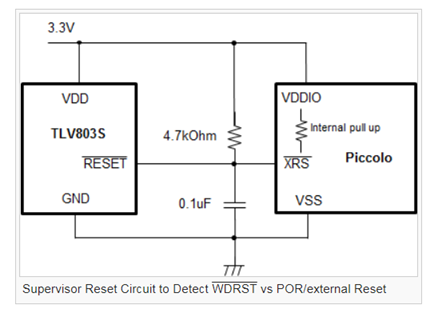

监控器 IC

漏极开路监控器 IC 可用作稳健的解决方案、该解决方案还可针对电源欠压情况提供保护。

POR 情况:监控器复位失效的延迟应足够长、以便使-XRS 保持低电平的时间超过3.7ms。

WDRESET 案例:使用开漏电路将允许-XRS 输出在512个 OSCCLK 周期内驱动为低电平、并在-XRS 以3.7ms 采样之前恢复为高电平以设置 WDFLAG。

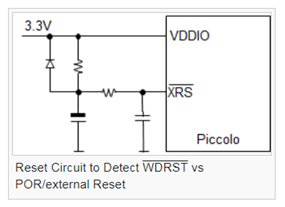

使用电容器和电阻器电路

- 可以使用大电容器电路、如图所示。

- 大电容将在 POR 事件期间保持低电平、在 WDRST 事件期间保持高电平。

- 3.3V 的上拉电阻器将上拉-XRS 引脚、以在上电后释放复位。

- 连接到 XRS 的串联电阻器将允许在 WDRST 事件期间将 XRS 完全驱动为低电平。

- 小电容器用于噪声滤波。

该二极管用于在断电时对 XRS 引脚放电。 在这种情况下、应在假设电容在3.3V 时充满电的情况下对二极管进行电流计算。 如果二极管无法处理放电电流、则可能需要一个与二极管串联的限流电阻器。

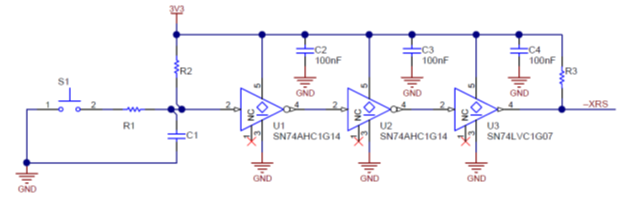

使用缓冲 R-C 电路

- 经缓冲的 R-C 电路将–XRS 引脚与大 C1在 WDRST 期间的影响隔离开来、但在上电/外部复位期间仍提供所需的脉冲宽度。

C2000培训小程序码