主题中讨论的其他器件:DP83822IF、 DP83822I、 DP83822HF、 DP83822H

大家好、我对 controlBoard 中的 clk 分布有疑问。

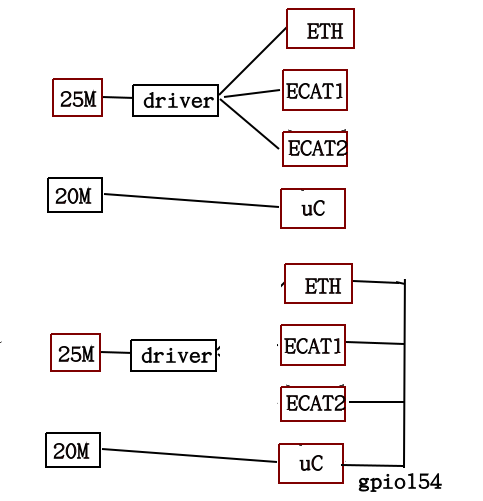

控制板使用外部时钟和时钟驱动器将时钟分配到 EtherCAT/以太网 PHY 和 uC。

问题是、如果 uC 具有多路复用功能、可以使用晶振/外部时钟和从 gpio154输出、为什么要这样做

我在这里粘贴了 controlBoard 实施细节、其中使用外部时钟和使用跳线的具有选择功能的驱动器、然后我在实施过程中仅使用一个直接耦合到 uC 的外部时钟、然后 PHY 使用引脚 gpio154。

我的方法是否正确? 是否正常工作? 选择一个或另一个的标准是什么?

提前感谢、致以诚挚的问候。

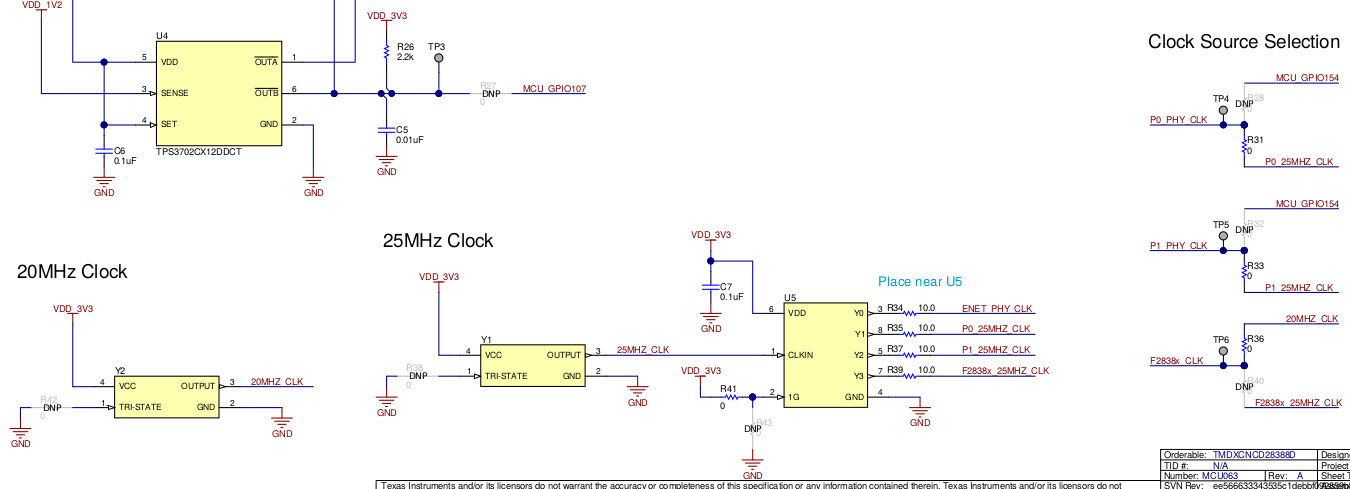

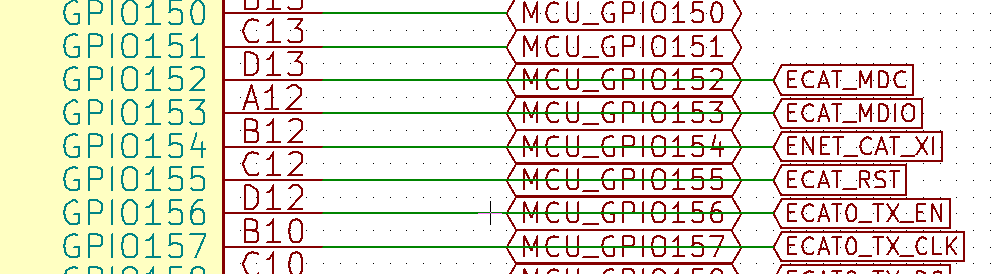

控制板 CLK 页面

控制板上的 CLK 分配。 一个外部 clk 和 clk 驱动器

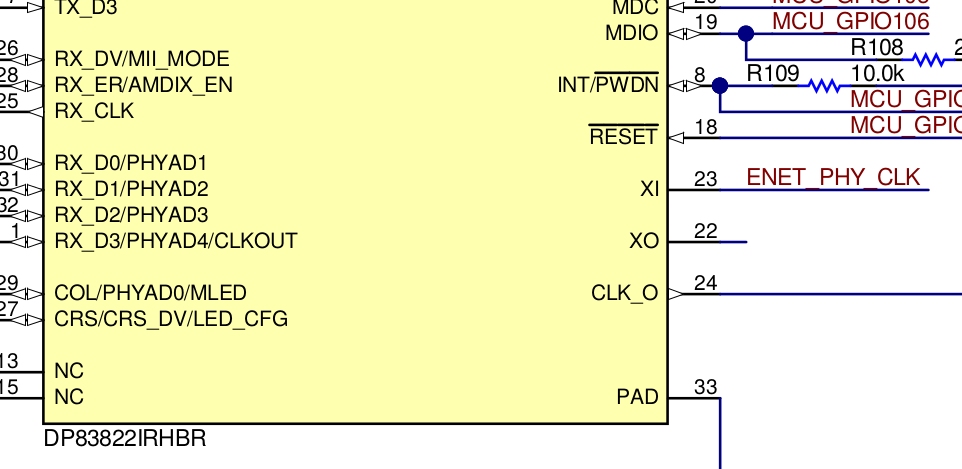

CLK 驱动程序->以太网

clk 直接来自驱动器、而不是来自 uC 引脚。

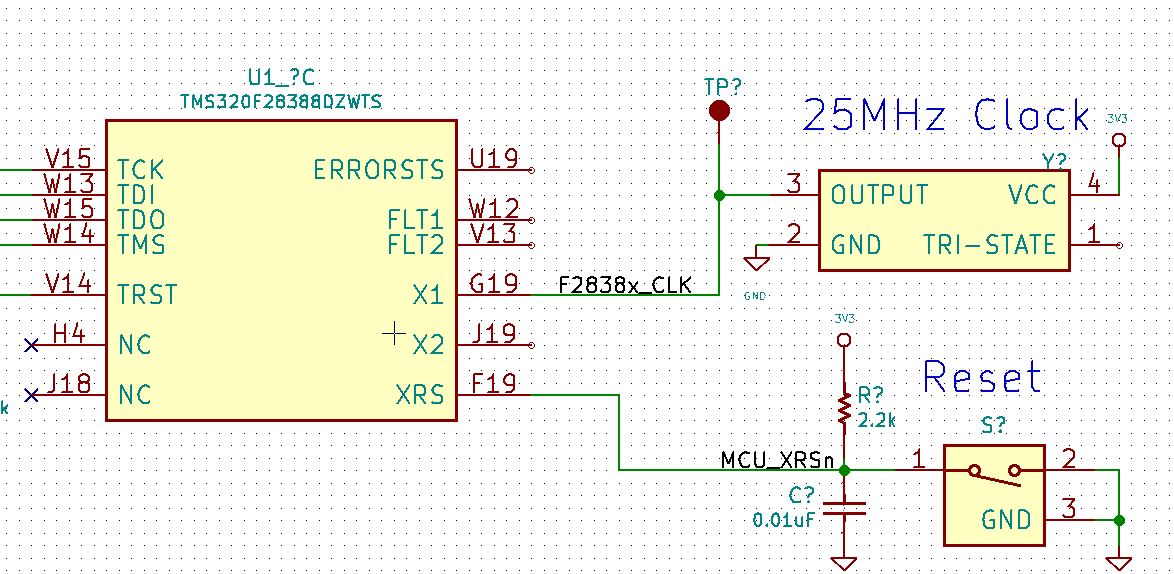

我的方法、将外部时钟 IC 连接到 uC、作为唯一的主系统 CLK

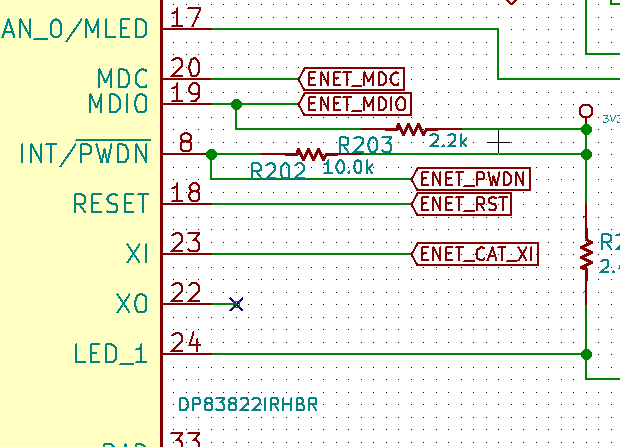

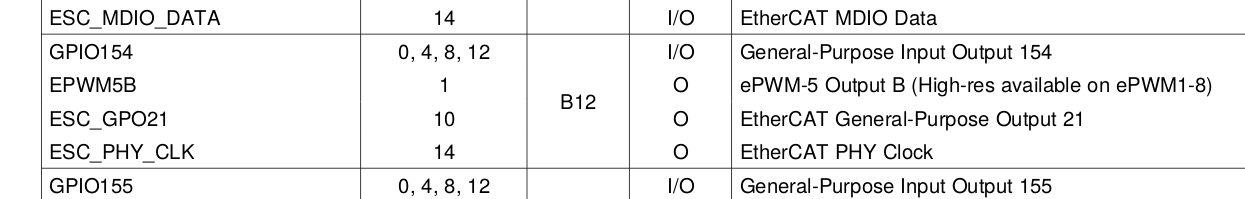

gpio156多路复用为 EtherCAT/以太网时钟->以太网 PHY 引脚 XI

Gpio154 uC 多路复用为 EtherCAT/以太网时钟(由固件提供)