工具/软件:Code Composer Studio

您好!

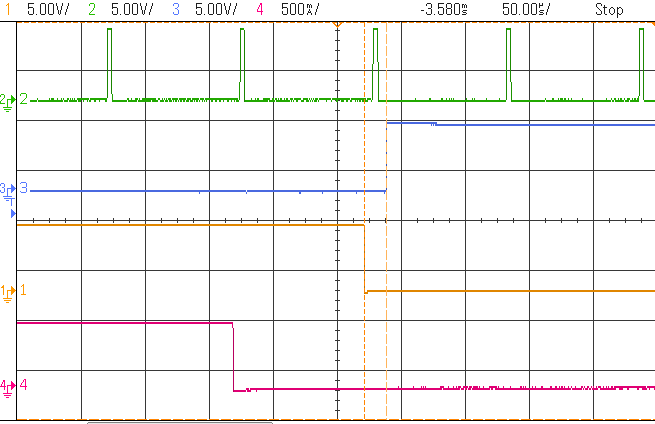

我观察到、当我向 CMPA 寄存器加载 EPWM 比较所需的变量时、下降沿的延迟大于上升沿的延迟。 粉色线是我要馈送到 CMP 寄存器的变量,它的低值为0,高值为1.2*TBPRD。 因此、我希望 ePWM 的输出波形(黄色)严格遵循我使用 DAC 显示的输入粉红色波形。 绿色脉冲表示 TBCTR 向上减计数器的过零、通过与0.1*TBPRD 进行比较显示为 ePWM 输出。

(请忽略下图中的光标(垂直虚线)、用"delay"表示粉色和黄色波形上升/下降之间的滞后)

上升沿:延迟少于一个 TBCTR 三角形周期

下降沿:延迟是 TBCTR 三角的一个周期

由于下降脉冲中的延迟与上升脉冲中的延迟相比增加、输出脉冲的宽度大于输入可变脉冲的宽度。 无论是否启用影子、都是如此。

如何最大限度地减小 EPWM 输出脉冲的延迟、以便将粉色和黄色波形之间的延迟降至最低?

如何确保两个边沿的延迟相同、从而使脉冲宽度不受影响?

谢谢

阿尔卡纳