请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TMS320F280049 主席/女士,

我使用 cmpss 模块通过 ePWM 交叉开关触发 ePWM 中的 tripzone。

我已经完成了以下设置。

AnalogSubsysRegs.CMPHPMXSEL.bit.CMP1HPMXSEL = 1;//O/C-N Cmpss1Regs.COMPCTL.bit.COMPHSOURCE = NEGIN_DAC; Cmpss1Regs.COMPDACCTL.bit.SELREF = reference_VDDA; Cmpss1Regs.DACHVALS.bit.DACVAL = 1862;// 1.5V cmps1Regs.CTRIPHFILCLKCTL.bit.CLKPRESCALE = 100; Cmpss1Regs.CTRIPHFILCTL.bit.SAMPWIN = 0x1F; Cmpss1Regs.CTRIPHFILCTL.bit.THRESH = 30;//3us Cmpss1Regs.CTRIPHFILCTL.bit.FILINIT = 1; Cmpss1Regs.COMPCTL.bit.CTRIPHSEL = CTRIP_FILTER; Cmpss1Regs.COMPCTL.bit.CTRIPOUTHSEL = CTRIP_FILTER; EPwm1Regs.TZDCSEL.bit.DCBEVT1 = TZ_DCBH_HI;//0x2 EPwm1Regs.DCTRIPSEL.bit.DCBHCOMPSEL = 0xF;//DCBHTRIPSEL EPwm1Regs.TZSEL.bit.DCBEVT1 = 1; EPwm1Regs.DCBCTL.bit.EVT1SRCSEL = DC_EVT1; EPwm1Regs.DCBCTL.bit.EVT1FRCSYNCSEL = DC_EVT_异 步; EPwm1Regs.DCBHTRIPSEL.bit.TRIPINPUT7 = 1; EPwmXbarRegs.TRIP7MUX0TO15CFG.bit.MUX0 = 0; EPwmXbarRegs.TRIP7MUXENABLE.bit.MUX0 = 1; EPwm1Regs.TZCLR.bit.OST = 1; EPwm1Regs.TZCLR.bit.CBC = 0; EPwm1Regs.TZCLR.bit.INT = 1; 系统时钟= 100Mhz

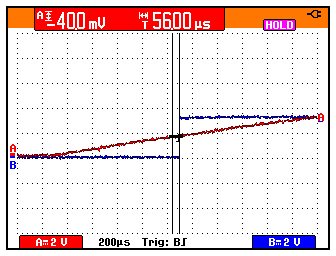

现在、当我在比较器输入上提供缓慢上升的信号时、跳闸延迟18毫秒。 当我提供相对较快的信号跳闸时、仅会延迟56微秒。

为了便于您参考、我附加了以下图片。

通道 A:比较器输入

通道 B:Tripzone 交叉连接

当快速更改比较器输入时、tripzone 会立即触发。

而在这两种情况下、电平设置为1.5V。

通道 B:比较器的输入

那么、请说明为什么该比较器输出延迟这么长时间?

谢谢

Rishabh