Thread 中讨论的其他器件:CCStudio、 controlSUITE、 TMS320F28075

工具/软件:Code Composer Studio

早上好。

在 CPU1配置后使用 CLA1时、我注意到一些问题。 我在 F28379D 目标上使用 CCStudio 7与 TI v6.4.2编译器[TI v16.9.1.LTS 会产生大量#2638错误:对齐

大于元素大小]。

无论如何、我的简单测试代码遵循 TI sketch、但它仅设置 CLA 上的 Task1、以便轻松更改本地 CLA 变量。 编译步骤是可以的;也是调试步骤

正确改进。

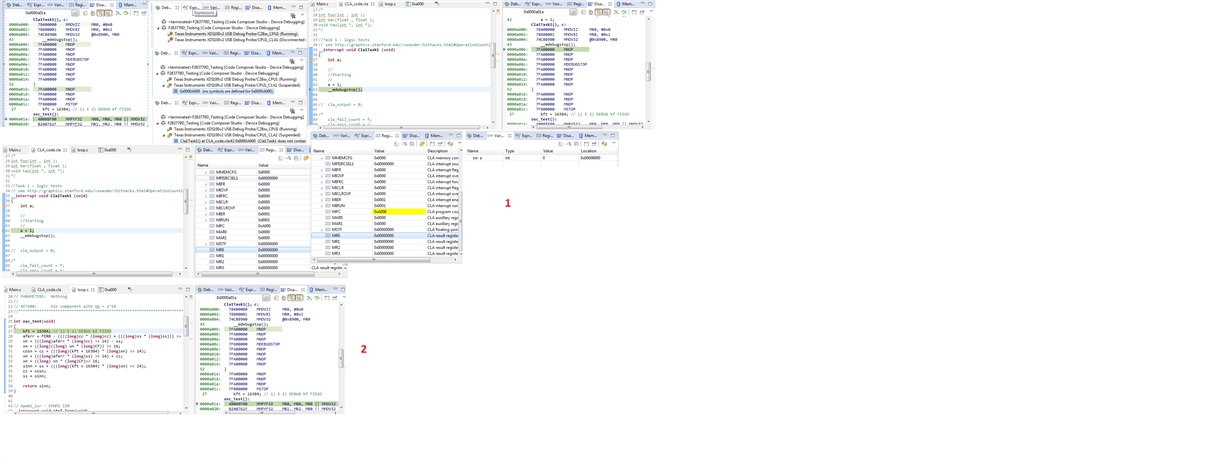

当我启动 CPU1代码时、在我在调试窗口 CPU1/CLA1中连接之后、CPU1执行自己的代码、直到在 Cla1ForceTask1andWait()函数:CPU1状态下等待

在焦点通过 CLA1时处于运行模式、CLA1处于挂起模式、没有为0x0000A000定义符号[我知道是由分配给 CLA1的原始 LS4-LS5 RAM

2837xD_RAM_CLA_lnk_CPU1.cmd]。 最后、当我在 CLA1上加载符号时、它会在'a = 1'的第一个 C 结构中停止。

接下来是通过 MSTOP 实现一个结构的汇编代码。

Cla1Task1()、c:

0000a000:78400000 MMOVIZ MR0、#0x0

0000a002:78800001 MMOVXI MR0、#0x1

0000a004:74C08900 MMOV32 @0x8900、MR0

43_mdebugstop();

0000a006:7FA00000 MNOP

0000a008:7FA00000 MNOP

0000a00a:7FA00000 MNOP

0000a00c:7F600000 MDEBUGSTOP

0000a00e:7FA00000 MNOP

0000a010:7FA00000 MNOP

0000a012:7FA00000 MNOP

0000a014:7FA00000 MNOP

52}

0000a016:7FA00000 MNOP

0000a018:7FA00000 MNOP

0000a01a:7FA00000 MNOP

0000a01c:7F800000 MSTOP

27kft = 16384;// 1) E 2)调试 KF Fisso

OSC_TEST():

0000a01e:40008F00 MMPYF32 MR0、MR0、MR0 || MMOV32 @0x8f00、MR0

这些问题与以下事件有关:

1) 1)如果我执行一个单步执行、MPC 到达0x000a006、而蓝色箭头指向__mdebugstop()函数。 MR0寄存器将被改变为1、然后它将被改变

加载到为'A'变量分配的 CLA1数据 RAM 中的0x8900中。 如果我在"Variable"窗口和0x8900 RAM 位置中选中 MR0、'A'、则看不到任何正确的值[它

保留0值]。 但是、如果我在"Variable"窗口或"Memory"中手动更改值、则会正确更改值。 CLA 的存储器似乎存在一些问题

但也具有自己的 MR0寄存器[???];

2) 2)如果我继续执行两个步骤、则 MPC 会超限 MSTOP CLA 结构并达到0x000a01e 程序位置、该程序位置将分配给 CPU1代码[????]。

是否有人澄清这种行为? 非常感谢。

迭戈。

PS:抱歉、我的英语不好。