你(们)好。

我在单端模式、12位分辨率下使用的是 DSP 28377D 中的 ADC 模块。 我想问您、您是否可以帮助确认我的 ADC 配置是否正确。

每个 ADC 配置如下:

void ConfigureADC_A (void) { EALLOW; //写入配置 AdcaRegs.ADCCTL2.bit.prescale = 0; AdcSetMode (ADC_ADCA、ADC_Resolution_12位、ADC_SIGNALMODE_SINGLE); //将脉冲位置设置为晚期 AdcaRegs.ADCCTL1.bit.INTPULSEPOS = 1; //为 ADC AdcaRegs.ADCCTL1.bit.ADCPWDNZ 加电 ;//允许 加电延迟1000 ms ;}

这里的问题是:通过设置

AdcaRegs.ADCCTL2.bit.prescale = 0;

我知道我在我的程序中设置了这个

ClkCfgRegs.PERCLKDIVSEL.bit.EPWMCLKDIV = 0

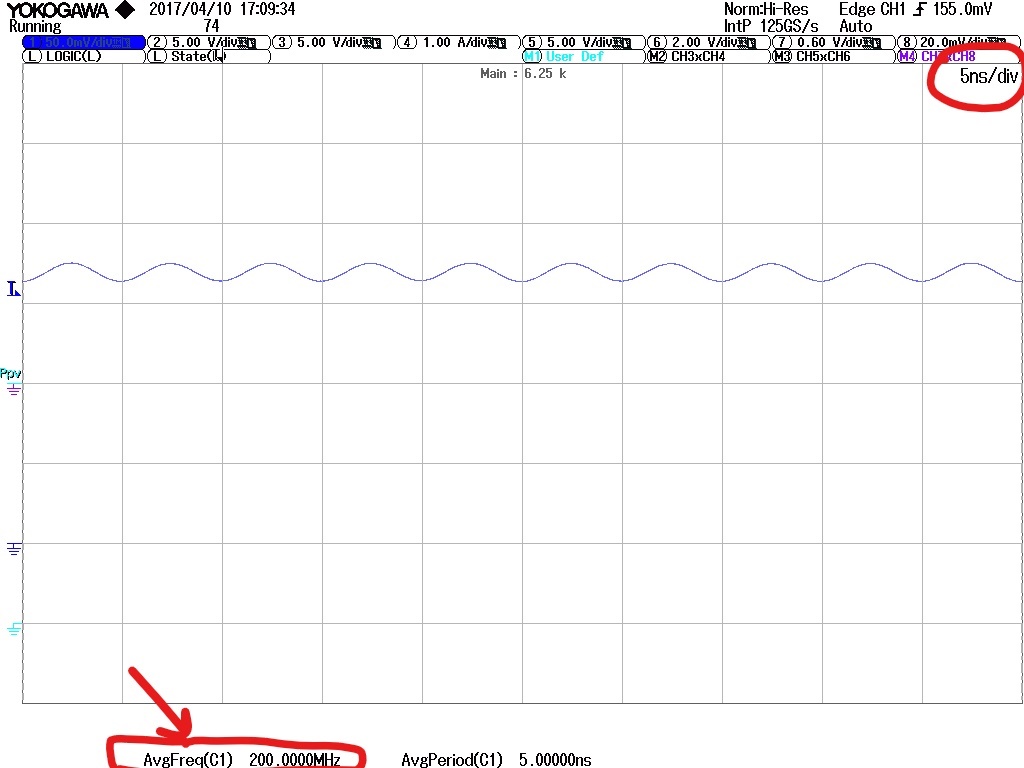

这是否意味着1x ADC 时钟周期= SYSCLK/1=(200MHz)^-1 = 5ns? 这看起来很小。

2. 我需要确认 ADC 参数 ACQPS 的计算正确。

我可以看到、在 SPRUHM8C (第1221页)文档中、TI 提供了有关如何大致估算采集窗口时间"t"的指南:

其中、右侧的 T 是采样保持电容器的充电时间常数。

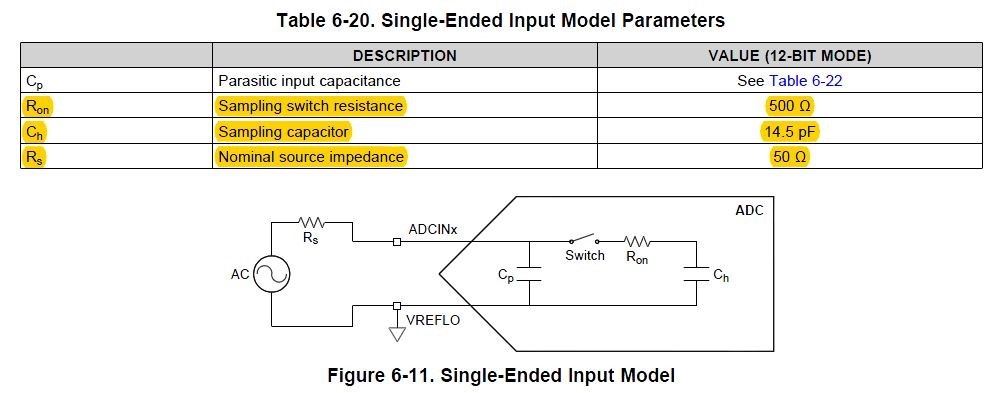

根据 SPRUHM8C (第1221页)中的建议和 数据表 SPRS880C (第107页、下面报告)中报告的 ADC 模型

然后:

T =(Rs+Ron)*通道

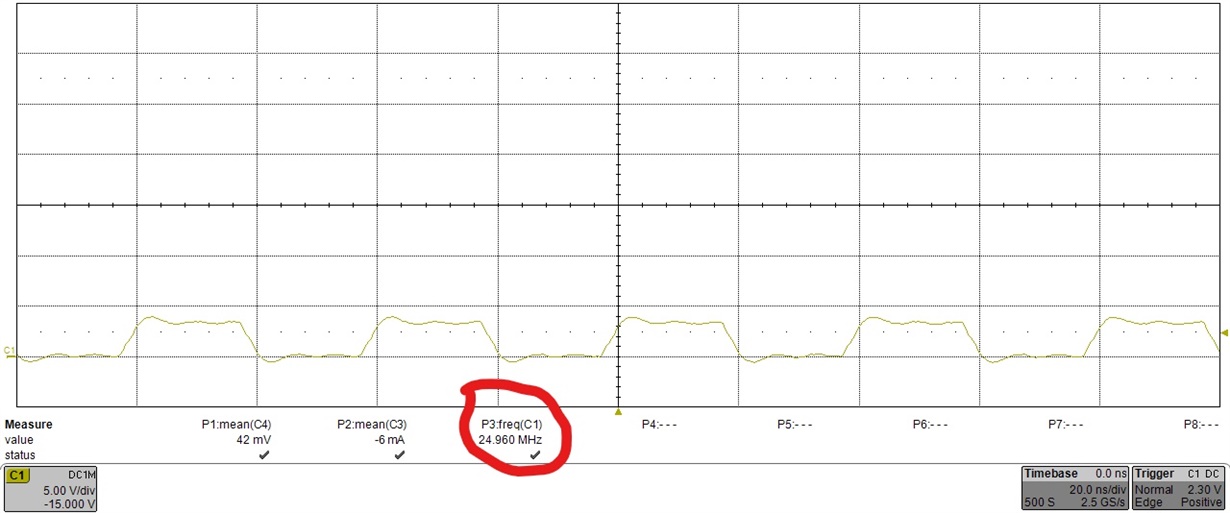

现在、在我的案例中、ADC 输入通过200欧姆电阻器连接到运算放大器的输出、如下图所示

我的问题是、我应该考虑 Rs = 200欧姆吗? 如果是这样、我计算 T =(500+200 Ω)*14.5pF = 10*10^-9s、采集窗口时间 t =-ln (0.25/2^12)*T = 100ns。

具有,t=100ns=(ACQPS+1)*SYSCLK --> ACQPS = 100ns/5ns -1 =19 (其中 SYSCLK=5ns,因为时钟为200MHz)。

总之、我提出了:

一个 ADC CLK = 5ns、如

AdcaRegs.ADCCTL2.bit.prescale = 0

2、ACQPS = 19、考虑数据表 SPRS880C (第107页)中给出的 Rs=200欧姆(ADC 输入和运算放大器输出之间的电阻)以及通道和 Ron。

您能否确认我的推理是否正确? 尤其是关于第2点、以及我在计算采集窗口时考虑的 Rs。

非常感谢你能抽出时间。

Leo