您好、香榭丽舍

我的客户有一个申请。 它们的产品 将并行使用。

它们使用 GPIO 引脚直接连接信号总线、作为波形结构图。

GPIO 管脚被配置为输出管脚、上拉 模块被禁用。

它们需要将一个 GPIO 初始设置为高电平、而另一个 GPIO 将下拉总线。

我们首先使用 GPIO 模块在单个单元上进行测试、并为电压不是零提供资金。

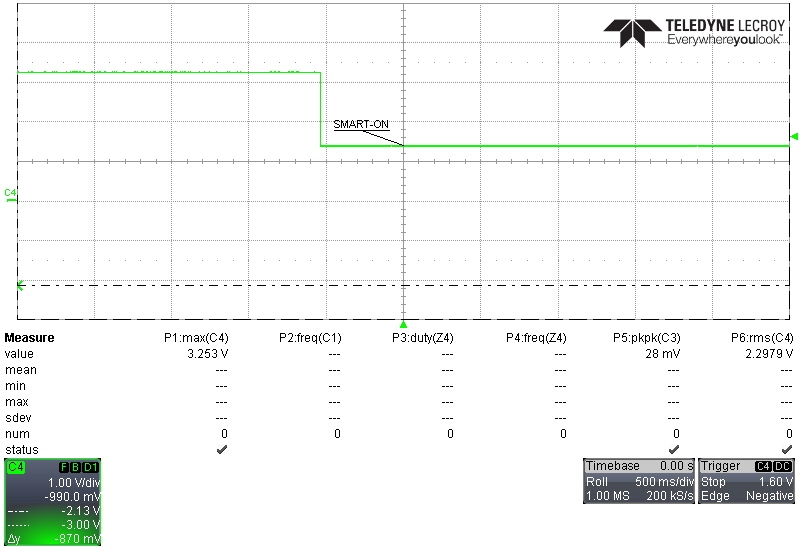

作为 波束波形、下降电压将保持在1.49V。

原始值为3.3V、 当我们清除另一个 GPIO DAT 值时、电压将降至1.49V。

在这种情况下, 一个是 GPIO12, 另一个是 GPIO31

但是、只有 GPIO18将下拉电压波纹1V。

客户想知道为什么 GPIO 无法真正将电压下拉至零、以及引脚之间存在差异的原因。

但是 ,C2000上的 GPIO 模块的方框图是什么?

您是否对配置有任何建议?

BR

Brian