主题中讨论的其他器件:OPA4350、 REF5030、 REF3030、 OPA350、 REF2030

您好!

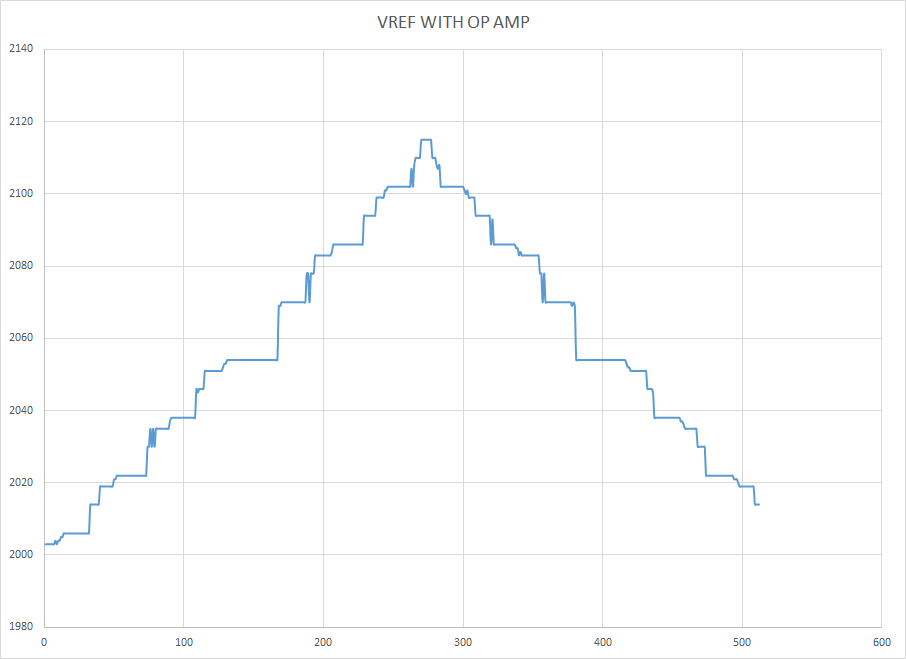

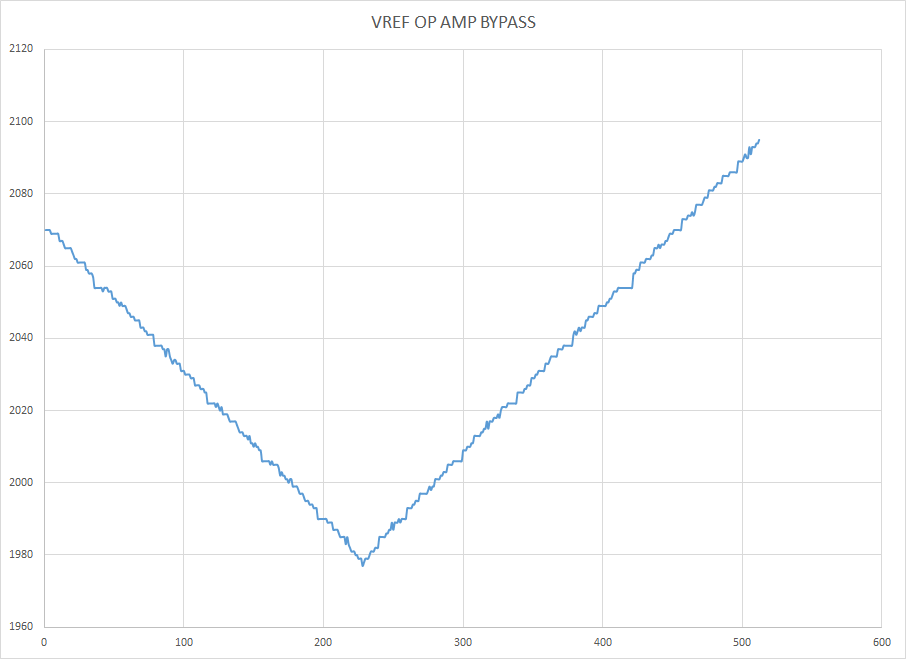

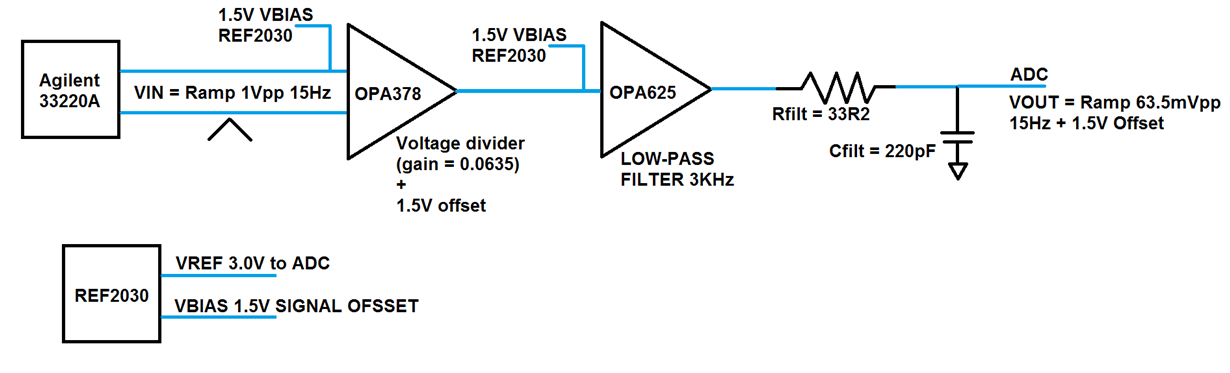

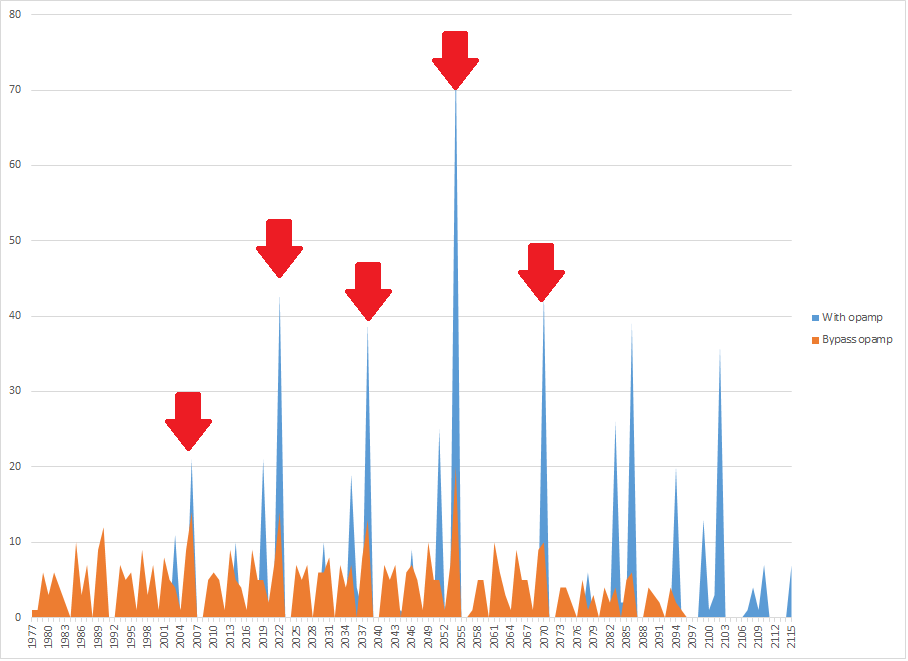

我在数天内遇到了 F2837x controlCARD R1.3的 ADC 转换问题、我认为我们发现了问题的根源。 Wewere 无法使用 ADC 获得良好的转换。 我们始终看到多个具有相同值的样本。 通过绕过3.0V 电压基准(U12 REF5030)的所有运算放大器(U13 OPA4350)、转换结果看起来非常好。 您能否确认问题来自开发板上的运算放大器。 您还能解释一下我们为什么在电路板上使用放大器获得这种结果。

链接至我以前的帖子:

此致

Dany