工具/软件:Code Composer Studio

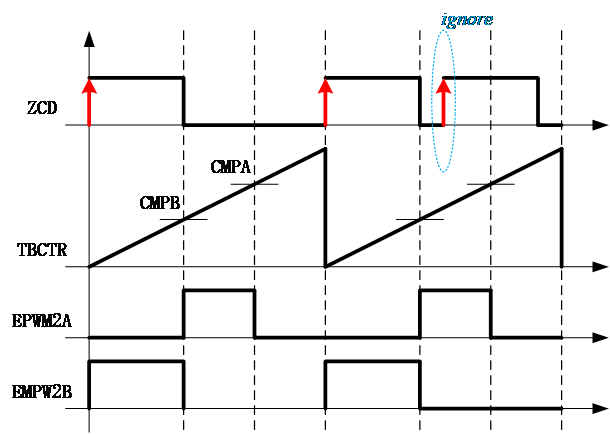

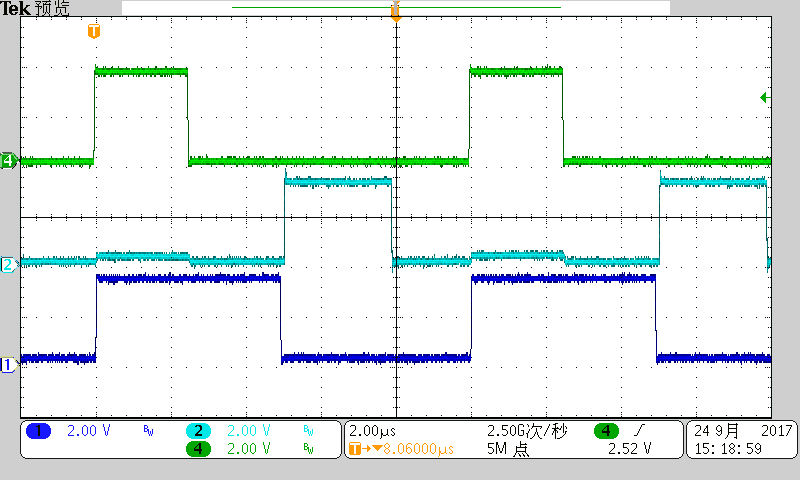

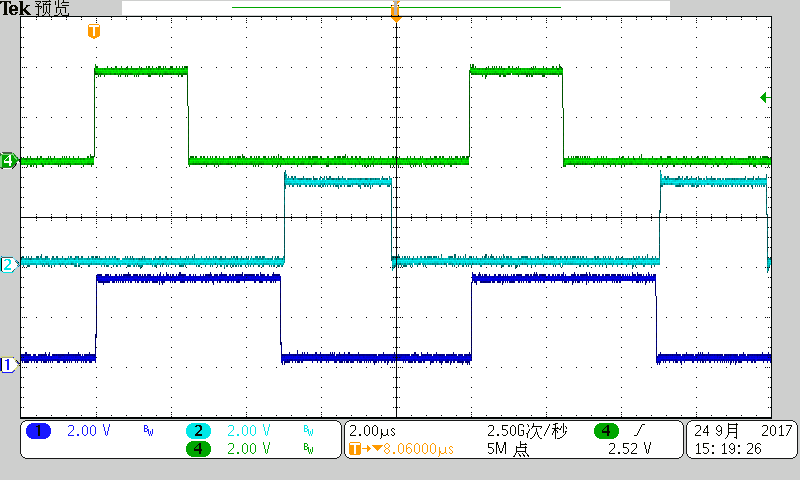

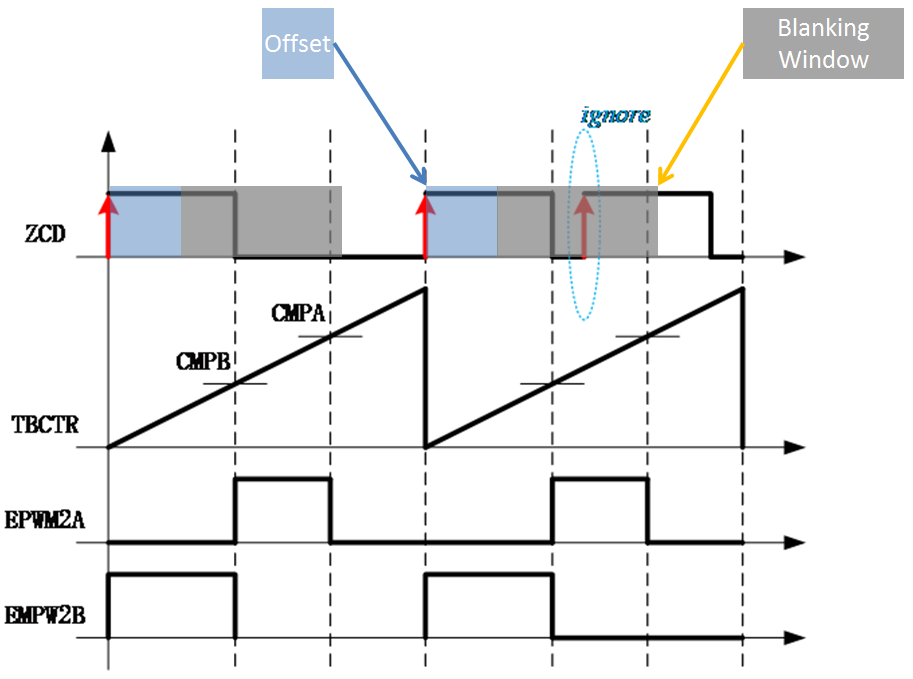

有一个 ZCD 信号输入 DSP、然后是 DSP 输出 EPWM2A 和 EPWM2B、它们的关系如图1所示。

图1.

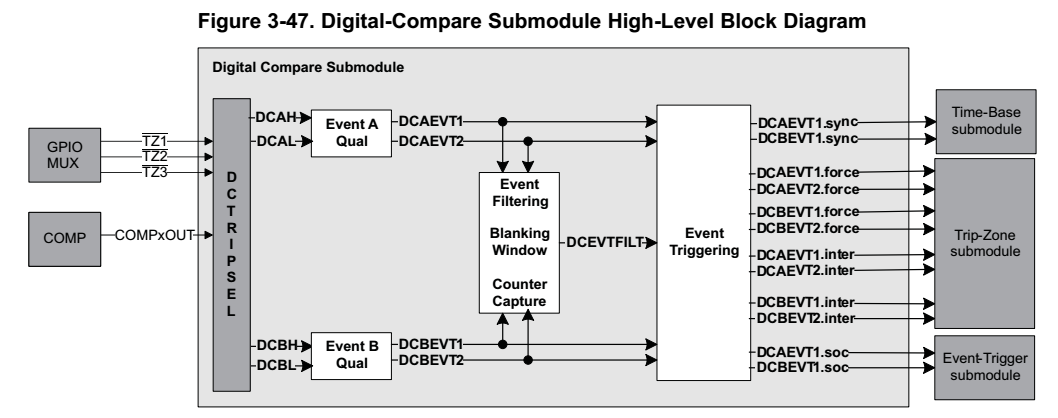

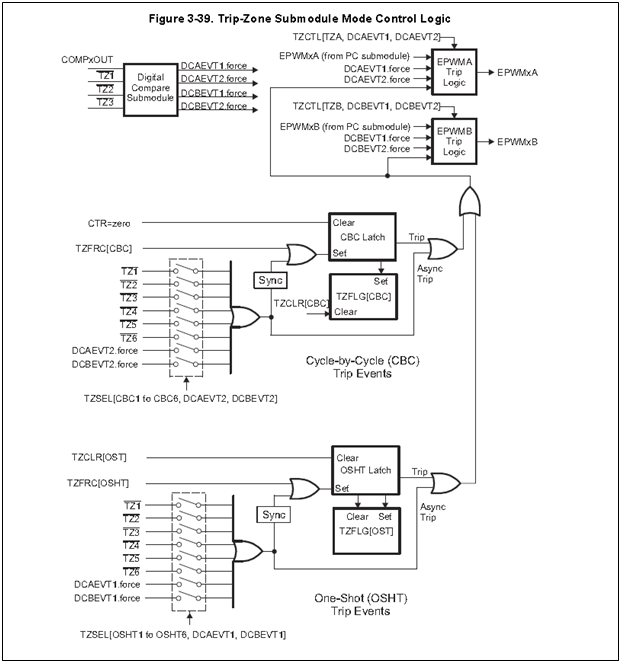

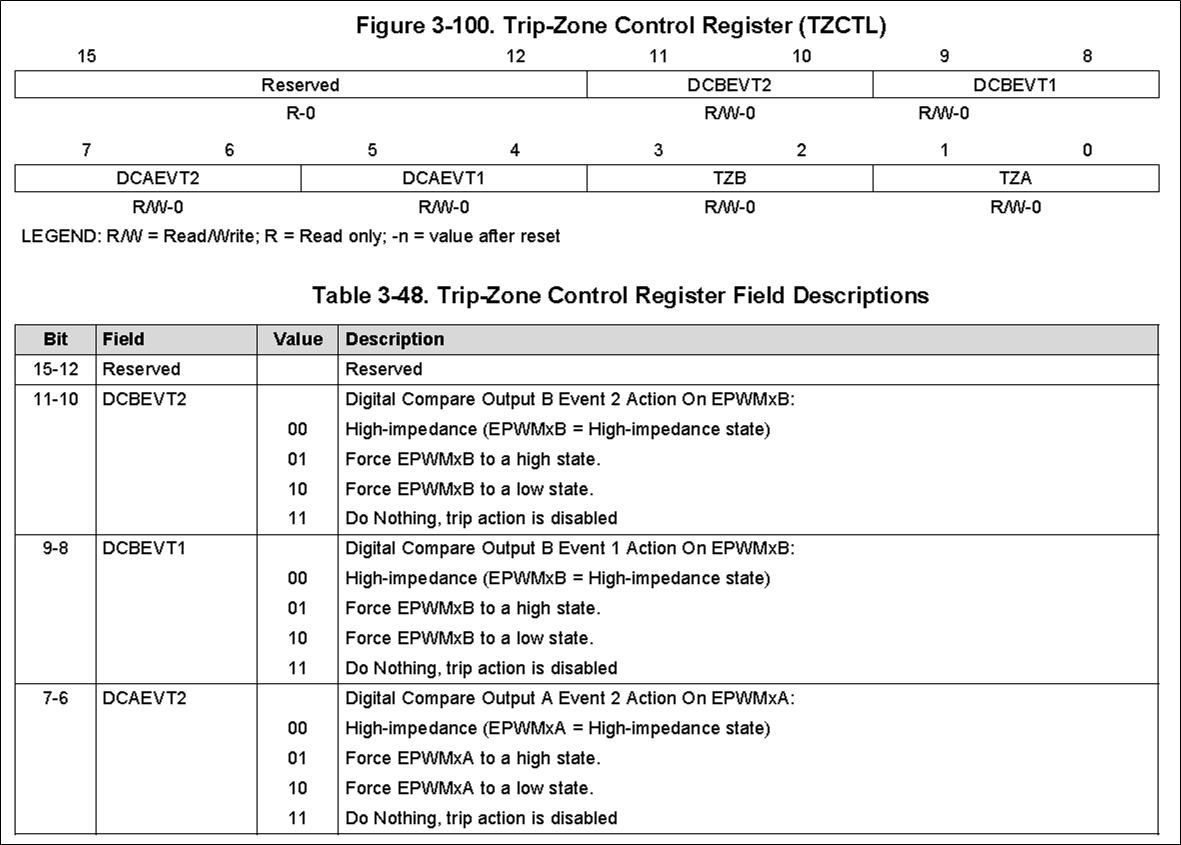

当 ZCD 的上升沿 ,EPWM2的数字比较(DC)子模块输出 DCAEVT1.SYNC,时、ZCD 连接到 DSP,的 TZ2 (GPIO13)引脚、如图3-47所示。 如果两个上升沿之间的时间太短、它可以使用消隐窗口来过滤 ZCD 的第二个上升沿。

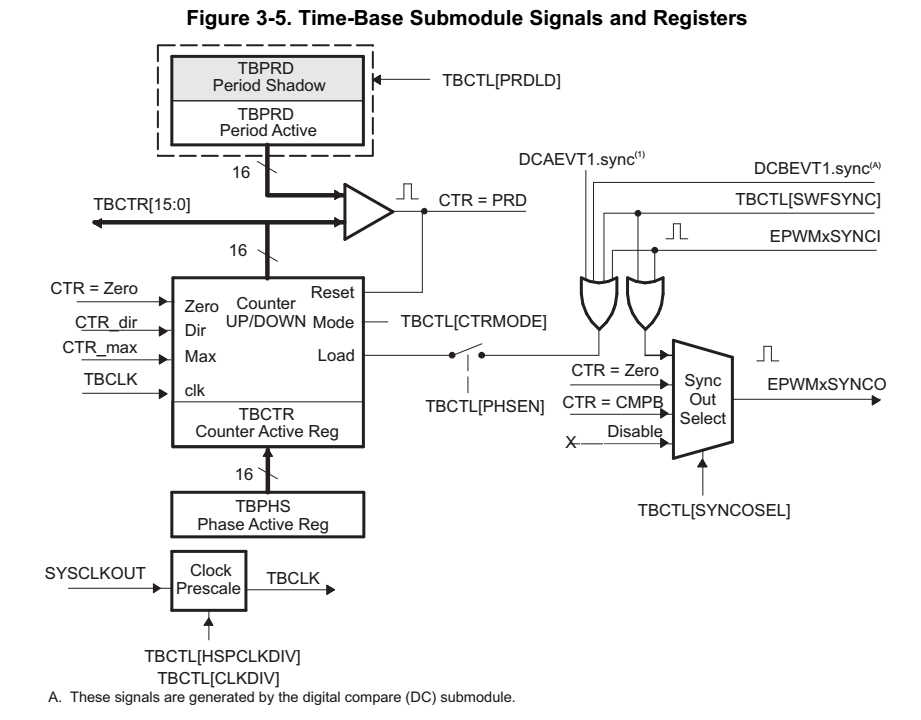

如图3-5所示、 DCAEVT1.SYNC 可以将 TBPHS 加载到 TBCTR、然后 TBCTR 从零增加。 当 TBCTR 被清零时、EPWM2B 被置位。 当 TBCTR 等于 CMPB 时、EPWM2B 被清零、EPWM2A 被置位。 当 TBCTR 等于 CMPA 时、EPWM2A 清零。

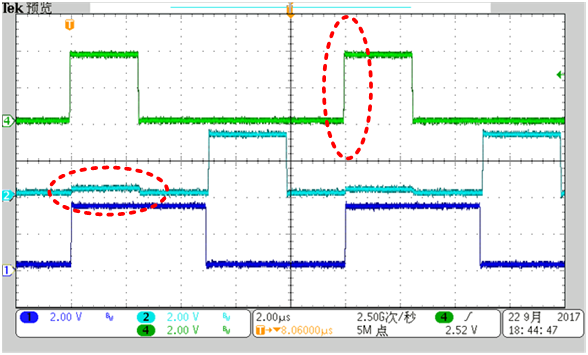

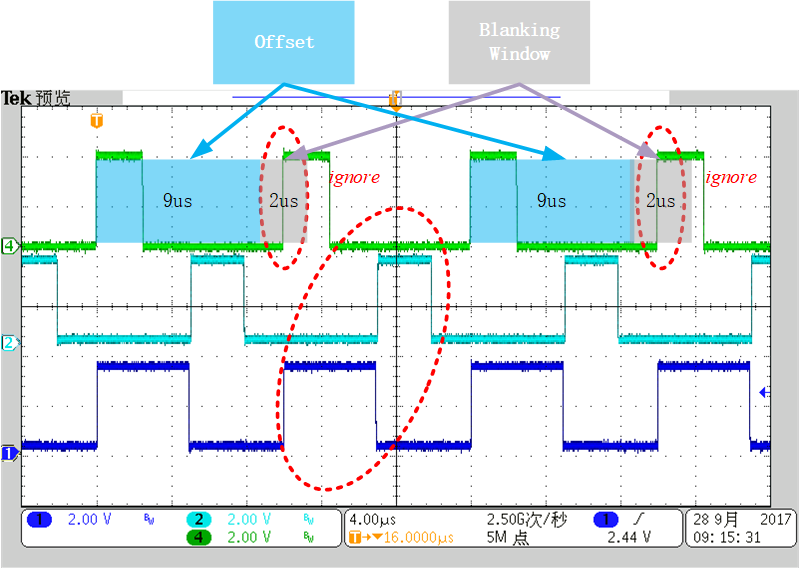

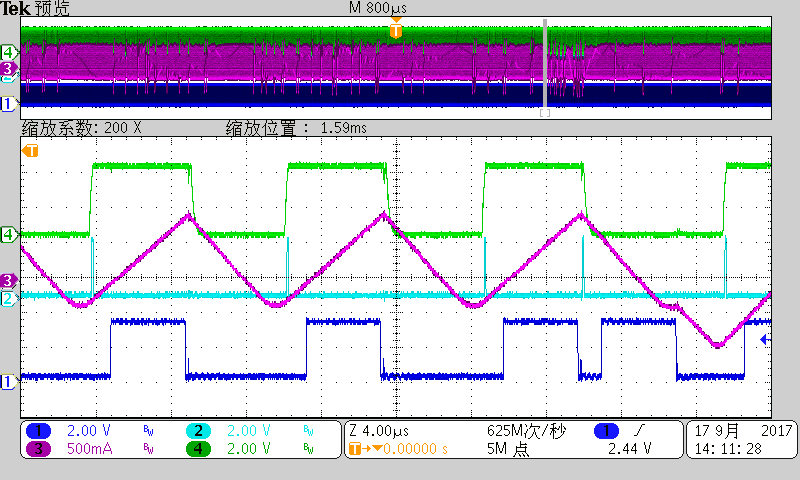

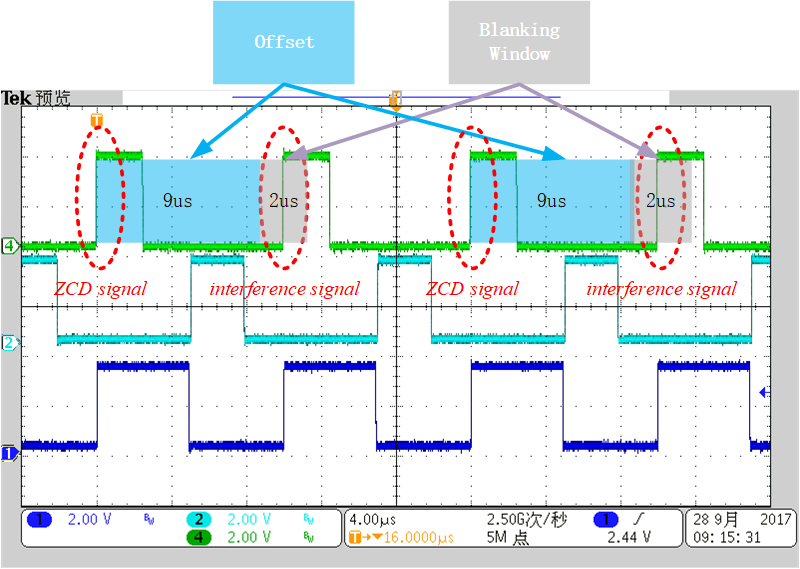

实验结果:

CH4 (绿色)是 ZCD、CH2 (浅蓝色)是 EPWM2A、CH1 (深蓝色)是 EPWM2B

有两个问题:

- 为什么 EPWM2A 在红色虚线框中不为0V、时间与 ZCD 的高级时间相同?

- ZCD 的第二个上升沿在第一个上升沿之后为10us。 在代码中、消隐窗口可以过滤 ZCD 的第二个上升沿、但在实验中它失败了、原因是什么?

有代码、硬件为 LAUNCHXL-F28069M:

#include "math.h"

#include "DSP28x_Project.h"

void InitEPwm2Examples(void);

int main (void){

InitSysCtrl(); //初始化系统控制

InitGpio(); //初始化 GPIO

InitEPwm2Gpio();

InitTzGpio();

//配置 ePWM 模块

EALLOW;

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC=0;

InitEPwm2Examples();

SysCtrlRegs.PCLKCR0.bit.TBCLKSYNC=1;

EDIS;

//等待 timer0中断

for (;;);

}

void InitEPwm2Examples(){

//设置 TBCLK

EPwm2Regs.TBCTL.bit.CTRMODE = 0x0; //向上计数模式

EPwm2Regs.TBPRD =4500; //设置计时器周期、在本示例中设置为最大值

EPwm2Regs.TBCTL.bit.PHSEN = 0x1; //启用相位加载

EPwm2Regs.TBPHS.Half.TBPHS = 0; //相位为0

EPwm2Regs.TBCTR = 0x0000; //清除计数器

EPwm2Regs.TBCTL.bit.HSPCLKDIV = TB_DIV1; //时钟与 SYSCLKOUT 的比率

EPwm2Regs.TBCTL.bit.CLKDIV = TB_DIV1;

//将影子寄存器加载设置为零

EPwm2Regs.CMPCTL.bit.SHDWAMODE = CC_SHADODE; //每0加载一次寄存器

EPwm2Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm2Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO;

EPwm2Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO;

//设置比较值

EPwm2Regs.CMPA.half.CMPA = 720; //设置比较值8us

EPwm2Regs.CMPB = 450; //设置比较 B 值5us

//设置操作

EPwm2Regs.AQCTLA.bit.CBU = AQ_SET; //强制 EPWM1A 输出为高电平;高电平开关打开

EPwm2Regs.AQCTLA.bit.CAU = AQ_CLEAR; //强制 EPWM1A 输出为低电平;高电平开关关闭

EPwm2Regs.AQCTLB.bit.ZRO = AQ_SET; //强制 EPWM1B 输出为高电平;低电平开关打开

EPwm2Regs.AQCTLB.bit.CBU = AQ_CLEAR; //强制 EPWM1B 输出为低电平;低电平开关关闭

//死区时间

EPwm2Regs.DBCTL.bit.IN_MODE = 0; //在事件 B 上清除 PWM1B、递增计数

EPwm2Regs.DBCTL.bit.HALFCYCLE = 0; //在事件 B 上清除 PWM1B、递增计数

EPwm2Regs.DBCTL.bit.POLSEL = 0; //在事件 B 上清除 PWM1B,递增计数

EPwm2Regs.DBCTL.bit.OUT_MODE = 2; //在事件 B 上清除 PWM1B、递增计数

EPwm2Regs.DBRED = 9; //在事件 B 上清除 PWM1B、递增计数0.1us

//直流

EPwm2Regs.DCTRIPSEL.bit.DCAHCOMPSEL = 1; //TZ2输入

EPwm2Regs.TZDCSEL.bit.DCAEVT1 = 2; //DCAH =高电平、DCAL =无关

EPwm2Regs.DCACTL.bit.EVT1SYNCE = 1; //同步生成启用

EPwm2Regs.DCACTL.bit.EVT1SRCSEL = 0; //0:源为 DCAEVT1信号;1:源为 DCEVTFILT 信号

//过滤器

EPwm2Regs.DCFCTL.bit.PULSESEL = 1; //时基计数器等于零

EPwm2Regs.DCFCTL.bit.BLANKINV = 1; //消隐窗口反相

EPwm2Regs.DCFCTL.bit.Blanke = 1; //消隐窗口被启用

EPwm2Regs.DCFCTL.bit.SRCSEL = 0; //源是 DCAEVT1信号

EPwm2Regs.DCFOFFSET = 810; //消隐窗口偏移9us

EPwm2Regs.DCFWINDOW = 180; //消隐窗口宽度2us

}