您好!

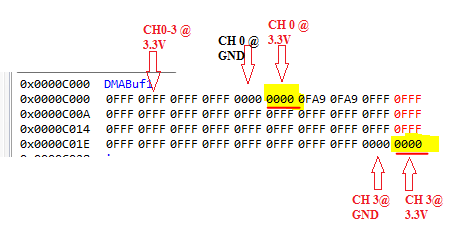

我将使用示例代码对 DMA 和 ADC 进行小型实验。 示例代码名为 Example_2833xAdcToDMA 、这将在 SEQ1中将 ADC 通道0转换为4并将其传输到 DMA。

现在、我已通过将 ADC 通道选择从8更改为4来更改代码小位。 此外、我还对 DMA 配置进行了如下必要的更改、

InitAdc ();//对于此示例,初始化 ADC //此示例的特定 ADC 设置: AdcRegs.ADCTRL1.bit.ACQ_PS = ADC_SHCLK; AdcRegs.ADCTRL3.bit.ADCCLKPS = ADC_CKPS; AdcRegs.ADCTRL1.bit.SEQ_CAS0_CASQ // 0非级联模式 AdcRegs.ADCTRL2.bit.INT_ENA_SEQ1 = 0x1; AdcRegs.ADCTRL2.bit.RST_SEQ1 = 0x1; AdcRegs.ADCCHSELSEQ1.bit.CONV00 = 0x0; AdcRegs.ADCCHSEVQ1 = 0x02 ;ADCCVSEQ1 = 0x1;ADCCONVREG1.ADC0001.ADC0001.ADCCVSEQ1 = 0x2;ADCONSELQ1 = 0x2 AdcRegs.ADCCHSELSEQ1.bit.CONV03 = 0x3; AdcRegs.ADCMAXCONV.BIT.MAX_CONV1 = 3;//设置 ADC 为每个 SOC 执行4次转换 //步骤5。 用户特定代码,启用中断: //初始化 DMA DMAInitialize(); //清除表 (i=0;i其余代码和设置相同。 我在这里面临的问题是、ADC 转换在第1次触发时正确放置在 RAM 中、而在第2次触发时、它放置了之前的 ADC 数据。 因此,ADC 结果在每次备用触发时都放置在 DMA RAM 中 。 可能的原因是什么? 是否可以仅将 ADC 用于前4次转换、在下一次触发时、转换将从 CH0开始?