我们有一个 SCID 驱动程序、该驱动程序在 CPU1上运行(即它传输数据)时可以正常工作、但当它必须在 CPU2上工作时、它不能工作。

要将 SCID 驱动程序移至 CPU2、我们已执行以下步骤:

一个示例

- SCID 的多路复用器配置

- 配置 DevConfRegs、以便为 SCID 放置 CPU2主器件

- GPIOCtrlRegs.GPCSEl4.bit.GPIO93 =0x2的配置

- GPIOCtrlRegs.GPCSEl4.bit.GPIO94 =0x2的配置

的示例

- PIE 矢量的初始化

- 配置了 CpuSysRegs、以便为 SCID 放置 CPU2主器件

- 完整的 SCID 配置(与 CPU1上的配置相同、包括 Tx 和 Rx ISR 设置)

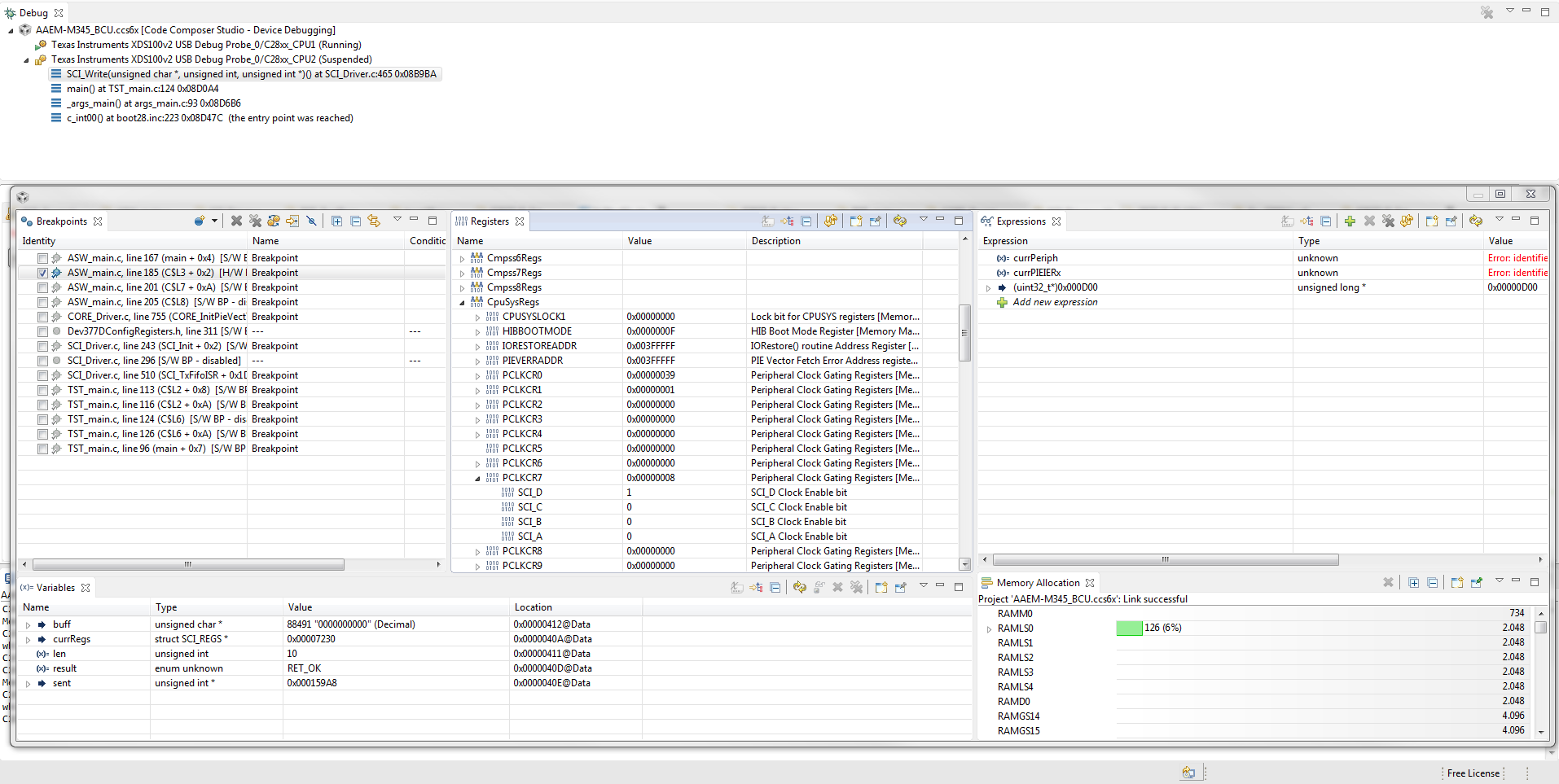

所有寄存器工作正常、但没有 Tx ISR 跳闸。

我注意到 CPU2上的 PIE 矢量表未更新。

我在哪里出错了?

顺便说一下、是否有处理这些问题的教程、即如何使用 CPU2上的外设所需的完整步骤列表?

谢谢、

Nicola