Other Parts Discussed in Thread: TMS320F28075, TMS320F28035

主题中讨论的其他器件: TMS320F28035

大家好、

我遇到的 HRPWM 问题与 本主题中提到的问题类似。 我在 TMS320F28035 (ePWM 1类)和 TMS320F28075 (ePWM 4类)上都看到了这种情况。

此问题表现为 PWM 输出上出现不必要的干扰。 在实际应用中、我使用了许多外设、例如 ADC、ECAP、ECAN、SPI、CPU 计时器和中断、CLA 等。但我花了一些时间找到了最小可能的代码、这使我能够重现问题、这似乎只涉及 ePWM 外设。

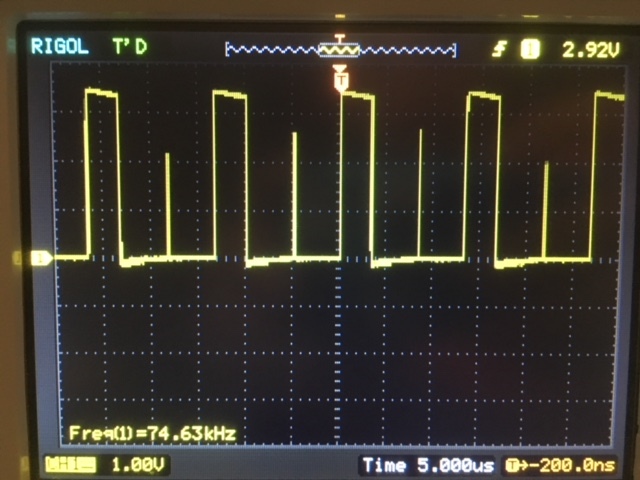

下面的示波器屏幕截图显示了干扰。 它是通过在 TMS320F28035 controlCARD 上运行的小型程序实现的。

GPIO0上的黄色信号是 EPWM1A。 蓝色信号是使用 EPWM2A 生成的基准信号、其边缘配置为事件 CTR = PRD 和 CTR = ZRO。

首先、请注意我尝试过的事项:

- ePWM 周期(TBPRD)和时钟速度(TBCTL[CLKDIV]和 TBCTL[HSPCLKDIV])似乎对问题没有任何影响。

- 我已经尝试过使用和不使用自动转换功能、但它似乎没有改变任何问题。

- 我已经尝试过使用 SFO ()函数的 MEP 后台校准,但似乎没有任何改变。

- 我已经尝试使用内部振荡器和外部石英、但它不会改变任何问题。

用于重现问题的代码如下所示:

EALLOW; SysCtrlRegs.PCLKCR1.bit.EPWM1ENCLK = 1; SysCtrlRegs.PCLKCR0.bit.HRPWMENCLK = 1; EPwm1Regs.TBCTL.bit.CTRMODE = 2; EPwm1Regs.AQCTLA.bit = 1;CAU = 1; EPwm1Regs.AQCTLA.bit.CAD = 2; EPwm1Regs.TBPRD = 200; EPwm1Regs.CMPA.half.CMPA = 50; EPwm1Regs.CMPCTL.bit.LOADAMODE = 1;// PRD 上的负载= EPwm1Regs.HRCMS.CMPAD.CLUS.CLUS.CLUS.CLUS.CLP= 0 ;EPwCMP1.THR1.TL.CLPAD.CLPAD.CLPAD.CLUS.CLPAD.CLPAD.CLPAD.1R1R1RGMES.CLP= 1;EPWCLPAD.CLPAD.CLPAD.CLPAD.CLP1.T1.T1.TL.R1CLPAD.CLPAD.CLPAD.CLPAD.CLPSRR = 1;EPWCLPAD.CLPAD.CLP1.T1.T1.T1.THR0.CLPAD.CLPAD.CLPAD.CLPAD.CLPAD.CLPAD. EPwm1Regs.CMPA.half.CMPAHR =(200U << 8); }

该程序所做的就是在零值和非零值之间切换 CMPAHR。

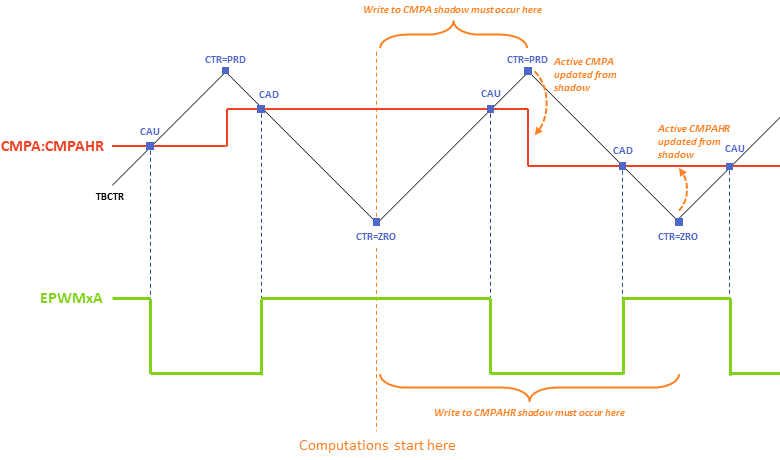

只有当 ePWM 以向上向下计数(TBCTL[CTRMODE]= 2)运行并且微边沿位置逻辑控制下降边沿(HRCNFG[EDGMODE]= 2)并且 CMPAHR 负载事件在脉冲之外被编程(当 PWM 信号为0时)时、这个问题才会出现。

最后一种情况是因为我在两种配置中看到了问题:

- 以 CTR=ZRO 为中心的脉冲(AQCTLA[CAU]= 1/AQCTLA[CAD]= 2 / HRCNFG[HRLOAD]= 1)

- 以 CTR=PRD 为中心的脉冲(AQCTLA[CAU]= 2/AQCTLA[CAD]= 1/HRCNFG[HRLOAD]= 0)

此外、干扰的宽度似乎与 CMPAHR 的值相关、如下面的两张图片所示。 第一个是 CMPAHR 设置为130步、第二个是 CMPAHR 设置为230步。

这就是我目前掌握的所有信息、但如果您需要了解任何其他信息、请告诉我。

谢谢、

皮埃尔