主题中讨论的其他器件:TMDSHSECDOCK

尊敬的 Sirs:

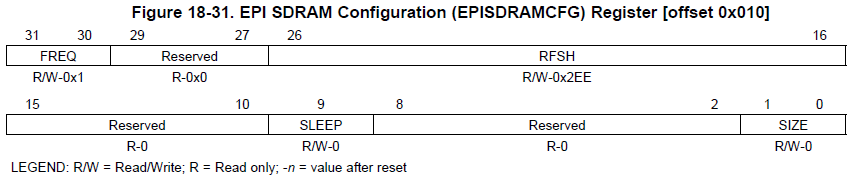

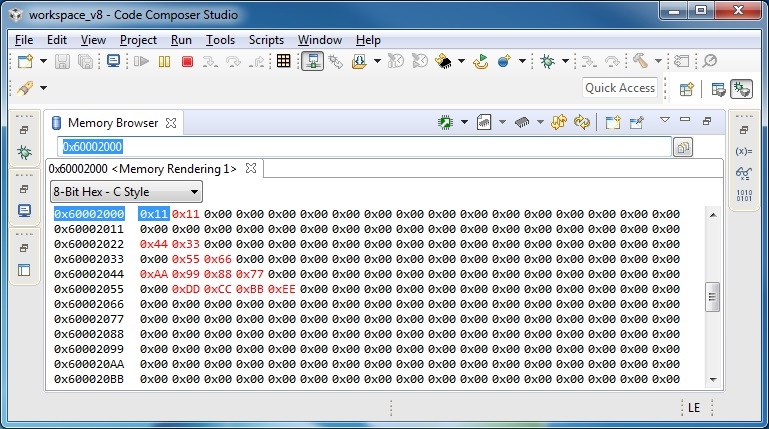

根据 SPRUHE8D.pdf 数据表的表18-1、我们已将 SDRAM 添加到 EPI 中。 我们使用的 SDRAM 芯片是 IS42S16800F 128Mbit (8M x 16)。 我们将其放置在0x60000000的基地址。 我们在控制套件中使用了 SDRAM 软件示例。 当访问16位和32位数据大小时、它适用于偶数地址。 但是、我们无法在奇数地址写入8位数据。 下面是我们问题的调试输出示例:

将0写入地址60002000 将1写入地址60002001 将2写入地址60002002

将3写入地址60002003

从地址60002000中读取0 从地址60002001中读取0 从地址60002002中读取2

从地址60002003中读取2

感谢你的帮助。