主题中讨论的其他器件:C2000WARE

您好!

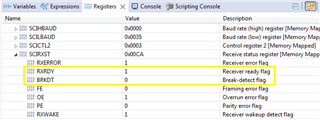

我一直 遇到由 sci.h 调用 driverlib SCI_getRxFIFOStatus()填充的 SCI RX FIFO 水平的奇数锁定问题。 RXFIFO 可用于一次16位填充、然后在 每次接收到多于16个字时随机锁定。 即使 使用阵列缓冲和返回状态阻止方法、也只有在后端才允许超过16个字。 RX FIFO 满电平 似乎只在禁用 ADCC1中断 RX 功能将 RX 缓冲区数据传递到多个编号缓冲区后的一个周期内有效。 RX FIFO ADCC1中的所有其他时间都比组9具有优先级、并且必须采用这种方式。

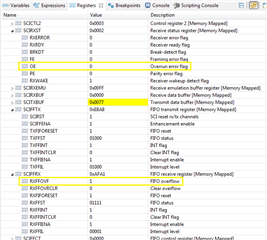

奇怪的是、ADCC1 ISR 处理程序仍然是闪烁的 LED、禁用 CPU 中断也被忽略。 因此、我有理由怀疑 FIFO 是否锁定且不发布任何 RX 异常消息。 ADCC1 INT 在 SCI RX/TX 中断处理程序中具有全局组优先级、并且试图清除 IER / IFR 标志的操作在子函数中只能进行一次。

编辑1/14/23:RX-FIFO 似乎锁定、不会触发 RX 溢出 INT、RXFFST 在 RXFFIL 寄存器事件匹配后不会清除位。

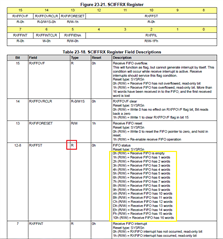

令我惊讶的是、SCIFFRx 寄存器中的呼叫大于8u。 硬件宏 IP 似乎位于 RXFFIL 位0的低8位字、>> 8u 至 NULL 地址空间。

也许 (hw_sci.h)中的(SCI_FFTX_TXFFST_M 8u)应该(<< 8)位于 RXFFST 以读取返回 FIFO 填充级别中的8-12位。

x49c CPU 是否会将寄存器从 MSB 15读取到 LSB 0? 硬件宏调用从右向左读回?

很抱歉、由于 ARM Cortex CPU 从位0至31读取寄存器、这似乎是所有 CPU 读取寄存器的正确方式。