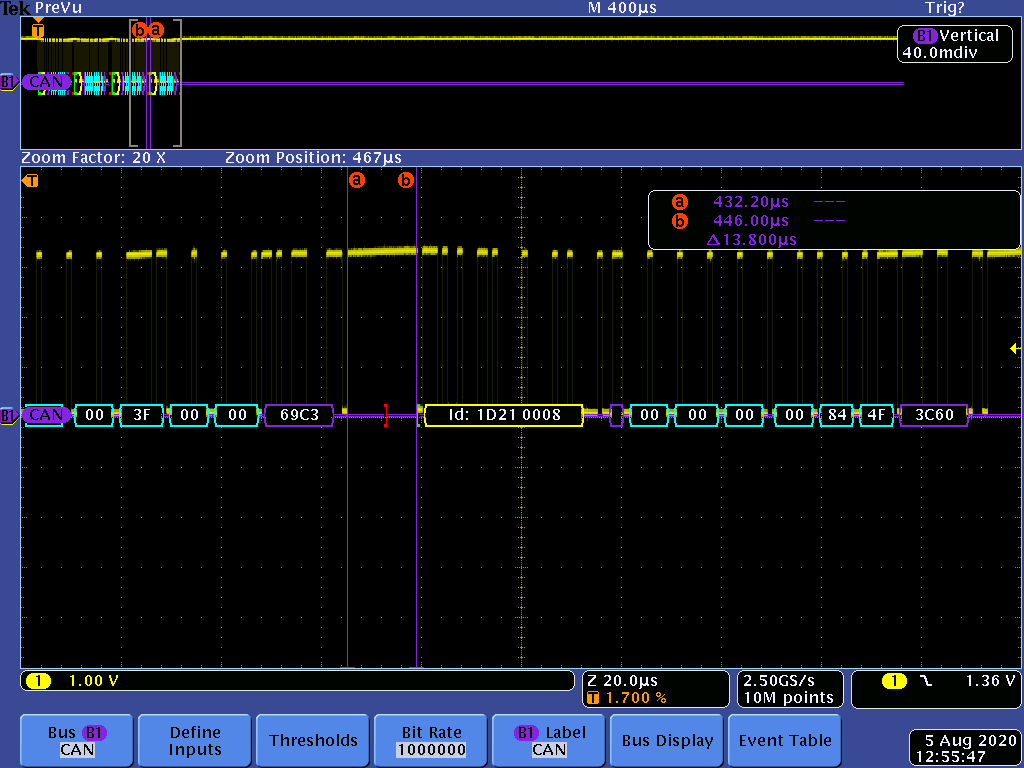

最近、我们更改了 TMS320F28374D 的 CAN 配置、以使用200MHz 外设时钟使用1Mbps 波特率。

现在、我们使用了 TExaS API 来初始化 CPU1和 CPU2中的 CAN 外设。 Moore、我们完全调用了函数

CANBitRateSet (GST_CAN[e_CANPort].u32_CANAddrBase、200000000L、1000000L);

通过这种方式、CAN 速率自动设置、使用19 (实数19+1)的时钟预分频器和以下参数(红色)

tatic const uint16_t g_ui16CANBitValues []=

{

0x1100、// TSEG2 2、TSEG1 2、SJW 1、除以5

0x1200、// TSEG2 2、TSEG1 3、SJW 1、除以6

0x2240、// TSEG2 3、TSEG1 3、SJW 2、分频7

0x2340、// TSEG2 3、TSEG1 4、SJW 2、8分频

0x3340、// TSEG2 4、TSEG1 4、SJW 2、9分频

0x3440、// TSEG2 4、TSEG1 5、SJW 2、10分频

0x3540、// TSEG2 4、TSEG1 6、SJW 2、分频11

0x3640、// TSEG2 4、TSEG1 7、SJW 2、12分频

0x3740 // TSEG2 4、TSEG1 8、SJW 2、分频13

};

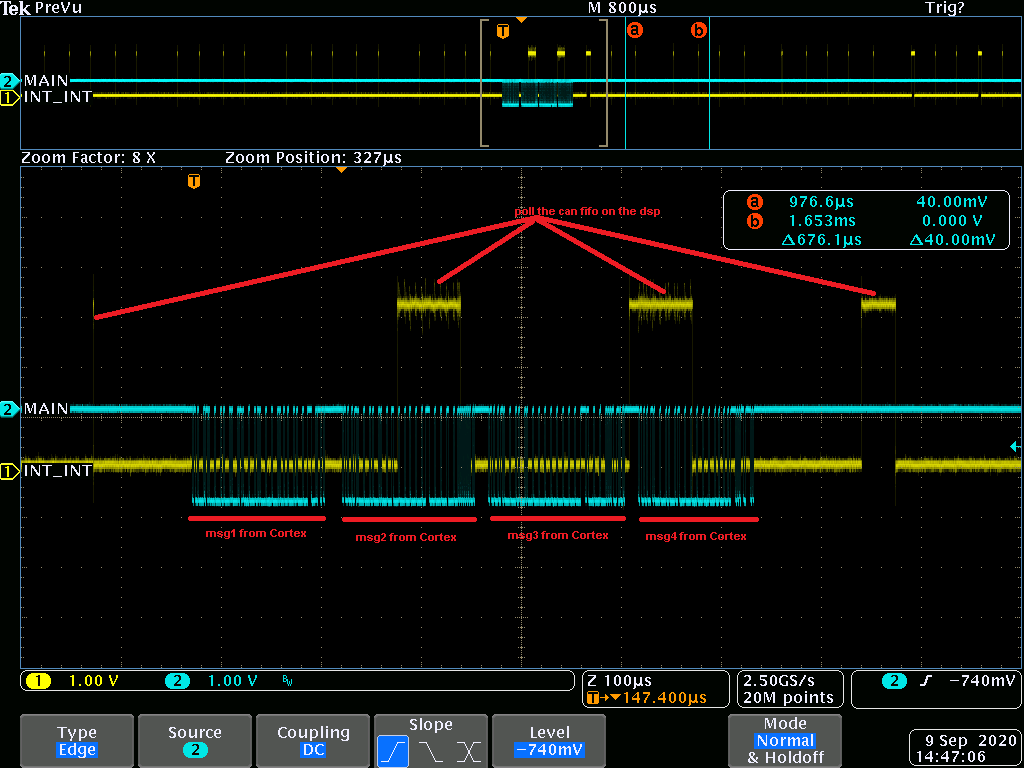

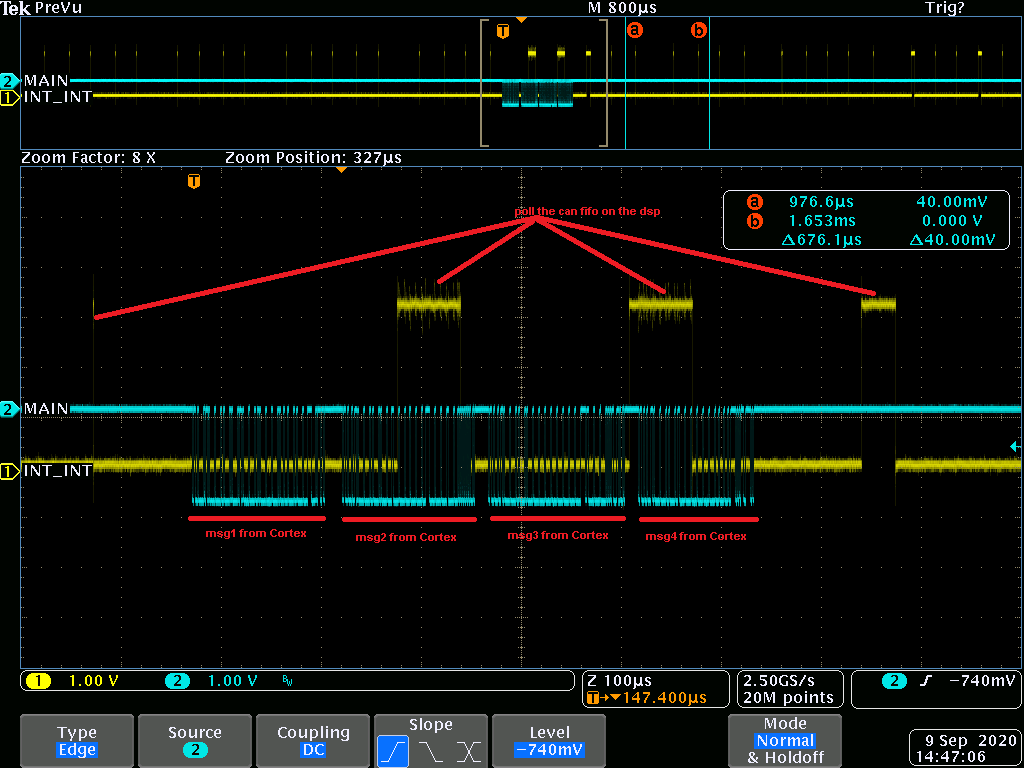

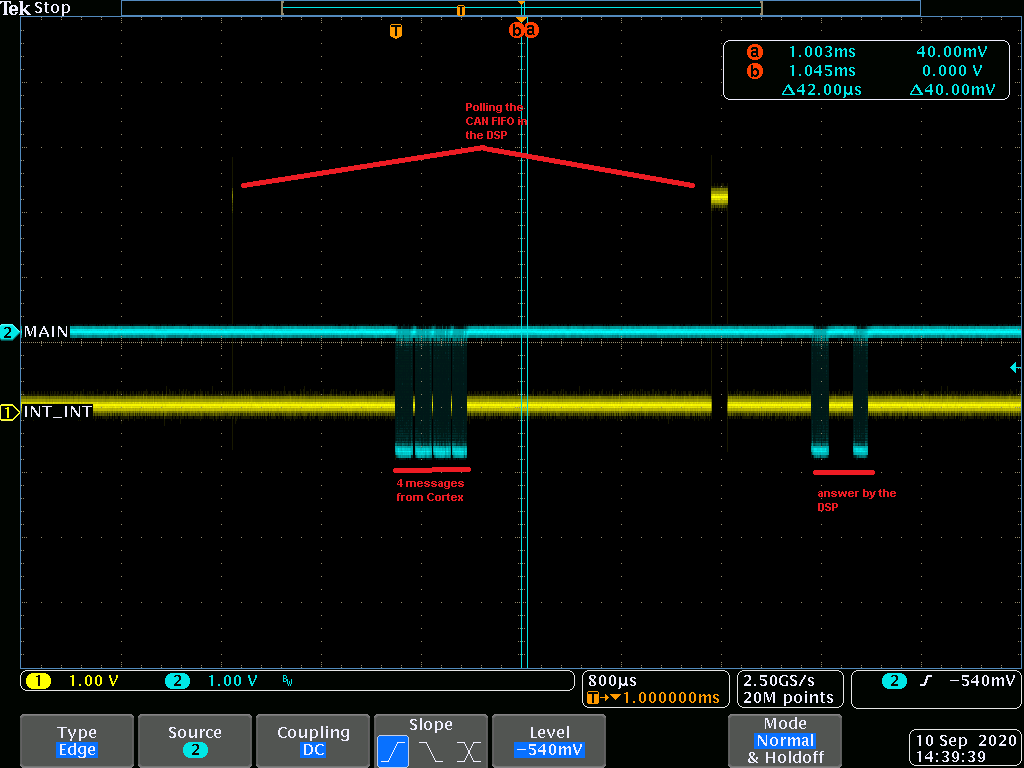

然而、一旦发送单元连续发送4条消息、彼此相差1uec、有时 DSP 丢失了1条消息。

CAN 队列是14个消息的深度、因此我们没有解释我们为什么要面临这一问题。

可以帮帮我们吗?

P.S.按照 mana 中的示例、我们已经尝试将配置寄存器设置为0x0700而不是0x3440、但问题仍然存在。 有时 DSP 不会收到消息。

感谢你的帮助、

Andrea Marcianesi。