主题中讨论的其他器件: TMDSDOCK28335

大家好、

我帮助客户提出问题。

"

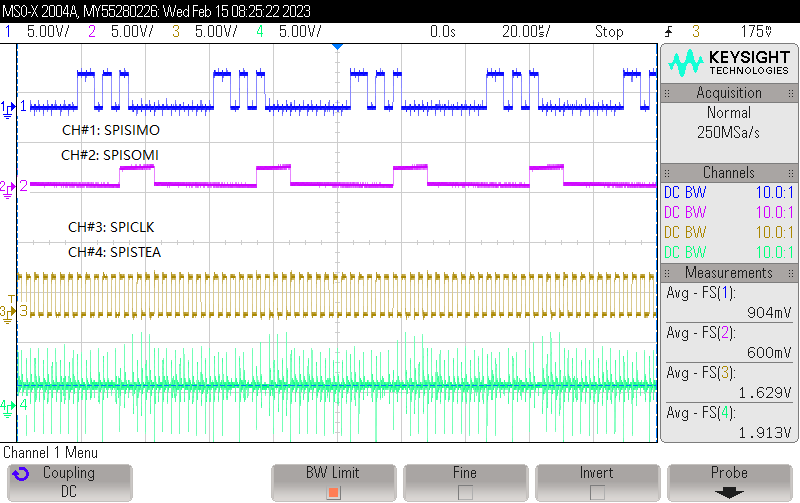

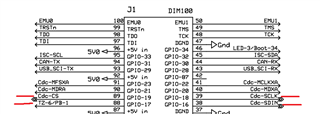

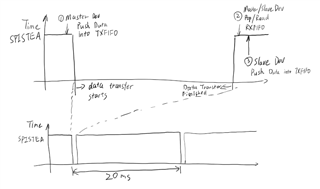

我正在尝试开始使用 F28335上的 SPI 功能。 现在、我将使用两 个带扩展坞的 TMDSCNCD28335控制卡。 在我尝试启动时、我计划在 SPI 中将板1用作主器件、并将板2用作从器件。 器件1将与第二个单元一起将时间数据发送到器件2。 器件2将仅向器件1发送0xF 的虚拟数据。 对于我的解串项目、我使用的是由 EPWMSOCA 触发的 ADC 中断、而不是 SPI 中断。 我修改了控制套件中的演示代码以完成此任务。 但它看起来器件1/2接收到的数据都是随机值、而不是我加载到发送器缓冲器中的值。 以下是我的 SPI 部分代码:

器件#1

void InitSpiFifoMaster() {/* 不带 FIFO*的初始化 SPI 从模式/SpiaRegs.SPICCR.bit.SPISWRESET = 0;//重置 SPI SpiaRegs.SPICCR.bit.SPICHAR = 0xF;//将 SPI charater 长度设置为16位(0xF) SpiaRegs.SPICCR.bit.SPICAR = 0>SPICTAL.SPICT.1>SPICT.MASTER.LE.SPICTRL.TAL.LE.SPICT.1> 发送。 设置为0将通过设置输出线路高 SpiaRegs.SPIBRR = 0x0063来禁用下一个字的 TX; //设置波特率:40MHz/(0x63+0x1)=40MHz/100=400bps SpiaRegs.SPIPRI.bit.FREE = 1;//启用自由运行、连续 SPI 操作、无论暂停发生 //*设置 SPI FIFO 寄存器*/ SpiaRegs.SPIFFTX.bit.SPIRST = 1;// 启用 SPIFFTX = 1;SPIFFIF.SPIF.SPIF.SPIF.SPIF.SPIFS/ SPIF.SPIF.SPIF.SPIF.SPIFFFIFO = 1;SPIF.SPIF.SPIF.SPIF.SPIF.SPIF.SPIF.SPIF.SPIF.SPIF.SPIF.SPIF.SPIFT. //从复位模式 SpiaRegs.SPIFFTX.bit.TXFFINTCLR 释放 TX FIFO = 1;//清除 TXFIFO 中断(W1C:写入以清除) SpiaRegs.SPIFFTX.bit.TXFFIL = 0x00;//将 TX FIFO 中断电平设置为0 FIFO SpiRegs.SPIFX.BIT = 1 ;RXIFFR.BIT = 1;接收 RXIFFRIFORT.TXT.TXIF.SIT.TXIF.SIT.SIT.TXT.SIT.SIT.SIT.SITX = 1; //清除 SPI FIFO RXFFINTCLR 标志(W1C:写入一个以清除) SpiaRegs.SPIFFRX.bit.RXFFIL = 0x0;//将 RX FIFO 中断电平设置为0 SpiaRegs.SPIFFCT.bit.TXDLY = 0x00;//将 FIFO 发送延迟设置为零 SpiaRegs.SPICESRCR.SPICESCR.bit 1; //从复位模式释放 SPI } void SpiTxDat (uint16 TX) { /*主器件发送到从器件的时间*/ GpioDataRegs.gpACLEar.gpio19 = 1; SpiaRegs.SPITXBUF = TX;//将数据加载到 SPI 输出缓冲 器,而(SpiDataRegs.SPIFX.gpiFET = 1)= 1;/SpiRXIF.GPIO= 1; //接收到数据!/SpiDataRegs.piRXIFx = 1;GPI = 1;GPI = 1;GPI 数据接收到数据

器件#2

void InitSpiFifoSlave() {/*Initializa SPI 从模式,不带 FIFO*/ SpiaRegs.SPICCR.bit.SPISWRESET = 0;//重置 SPI SpiaRegs.SPICCR.bit.SPICHAR = 0xF;//将 SPI charater 长度设置为16位(0xF) SpiaRegs.SPICCR.bit.SPICAR = 0>SPICTAL.SPICT.USTRL.1>SPICTAL.LE.SPICT.USTRISTALM.0 ;/SPICT.USTRISTL.BIT.1<bit.SPICTALT.0;/SPICTALT. 设置为0将通过设置输出线路高 SpiaRegs.SPIBRR = 0x0063来禁用下一个字的 TX; //设置波特率:40MHz/(0x63+0x1)=40MHz/100=400bps SpiaRegs.SPIPRI.bit.FREE = 1;//启用自由运行、连续 SPI 操作、无论暂停发生 //*设置 SPI FIFO 寄存器*/ SpiaRegs.SPIFFTX.bit.SPIRST = 1;// 启用 SPIFFTX = 1;SPIFFIF.SPIF.SPIF.SPIF.SPIF.SPIFS/ SPIF.SPIF.SPIF.SPIF.SPIFFFIFO = 1;SPIF.SPIF.SPIF.SPIF.SPIF.SPIF.SPIF.SPIF.SPIF.SPIF.SPIF.SPIF.SPIFT. //从复位模式 SpiaRegs.SPIFFTX.bit.TXFFINTCLR 释放 TX FIFO = 1;//清除 TXFIFO 中断(W1C:写入以清除) SpiaRegs.SPIFFTX.bit.TXFFIL = 0x00;//将 TX FIFO 中断电平设置为0 FIFO SpiRegs.SPIFX.BIT = 1 ;RXIFFR.BIT = 1;接收 RXIFFRIFORT.TXT.TXIF.SIT.TXIF.SIT.SIT.TXT.SIT.SIT.SIT.SITX = 1; //清除 SPI FIFO RXFFINTCLR 标志(W1C:写入一个以清除) SpiaRegs.SPIFFRX.bit.RXFFIL = 0x0;//将 RX FIFO 中断级别设置为0 SpiaRegs.SPIFFCT.bit.TXDLY = 0x00;//将 FIFO 发送延迟设置为零 SpiaRegs.SPICF.SpiSpi1.SPICF = 0x00;同时将 SpiF = 0xSpiRF.SPIRF.SPIRF.SPIRF.SpiSpiSpiSpiSpiSpiSpiSpiSpiSpin.***.SpiSpin.SPCR.SpiSpiSpiSpiSpiSpiSpiSpin.SPIF.SpiSpiSpiSpiSpin.Spi //等待数据被接收 DataSpiRx = SpiaRegs.SPIRXBUF; }

我不确定我的代码中哪种设置是错误的。

"

非常感谢你的帮助。

此致、