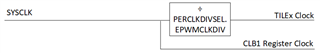

从 E2E 设计支持论坛、我可以获得 CLB 的最高频率为100MHz 的信息、并且该信息通过 分频器计时到 ePWM。

来自:e2e.ti.com/.../launchxl-f28379d-launchxl-f28379d-clb-clock-frequency

基于这些信息、我有以下问题

1. ePWM 的最高工作频率为200MHz。 ePWM 模块有许多到 CLB 的输出。 这是最高频率为200MHz 的信号输出。 ?如何配置 CLB 来保证 CLB 模块(100MHz)可以处理来自 EPWM?的输入信号、或者如果信号时序宽度小于 CLB 时序周期、CLB 无法处理这种情况

2.从表26-2中我还发现 CLB 具有来自 ECAP/CPU 输出的本地输入、工作频率可能为200MHz? 我如何为这些输入信号配置 CLB?