您好!

在数据表 I2C 时序要求表中、我们仅列出了标准模式下 I2C SDA 和 SCL 的最大上升和下降时间要求。 但是、在快速模式下、我们还列出了这两个信号的最小上升和下降时间要求。

如果我们测量 SDA/SCL 信号的下降时间、则下降时间小于1us、这违反了数据表中的最小时序要求。 我的问题是、I2C 主设备和/或从设备的最短上升/下降时间是多少? 如果违反最小时序、I2C 模块和 I2C 模块是否需要无法通信?

谢谢。此致、

Luke

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

在数据表 I2C 时序要求表中、我们仅列出了标准模式下 I2C SDA 和 SCL 的最大上升和下降时间要求。 但是、在快速模式下、我们还列出了这两个信号的最小上升和下降时间要求。

如果我们测量 SDA/SCL 信号的下降时间、则下降时间小于1us、这违反了数据表中的最小时序要求。 我的问题是、I2C 主设备和/或从设备的最短上升/下降时间是多少? 如果违反最小时序、I2C 模块和 I2C 模块是否需要无法通信?

谢谢。此致、

Luke

Luke、

I2C 上升时间/下降时间适用于控制器(主器件)和目标器件(从器件)。

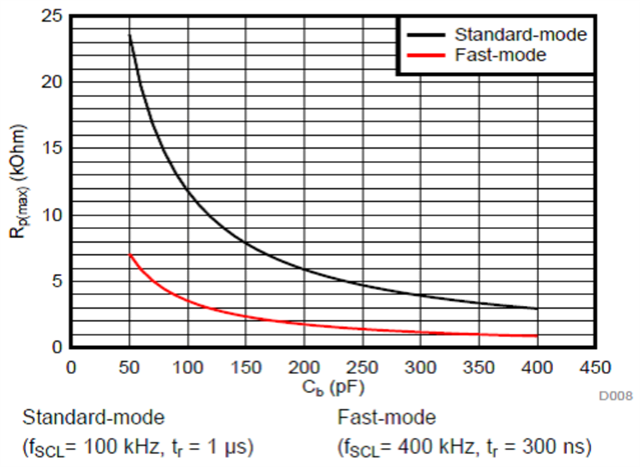

1us 的下降时间绝对违反 I2C 规范、您显然会在规范之外运行。 您使用的总线电容和外部上拉电阻器是什么? 如果您的下降时间如此慢、您所使用器件的灌电流能力如何。

使用大约2.2k Ω 的更强拉电阻器总是更好、并且提供更好的抗噪性能、还允许在给定的 I2C 速度下(标准模式与快速模式)产生高总线电容。

此致、

Manoj

Manoj,

抱歉、出现了拼写错误和混淆。

是指在数据表中、我们列出了 最小值 下降时间要求为11.4ns、 最小值 对于 I2C 快速模式、上升时间要求为20ns。 在 实际测量 SDA 和 SCL 信号时、下降时间和上升时间通常小于 1ns 例如 600ps 。 这违反了数据表中的下降时间和上升时间最小要求。

我的问题是、I2C 快速模式是否真正需要最短 SDA/SCL 下降时间和上升时间? 如果下降/上升时间小于数据表中的最低要求、是否存在任何问题?

此致、

Luke