主题中讨论的其他器件:TIDM-02009、 PMP23126

您好、Gus:

我将 PCMC 软件加载到 PSFB CDR 板。 TR 导联拓扑的 I DRIVE 开关、QD 结束电源传输间隔。 我研究了 TIDM-02009、PMP23126的软件。

我将测试 唯一的内部环路性能、因此我通过 UART 更改了 MAXREF 值并更改了峰值电流设定值。

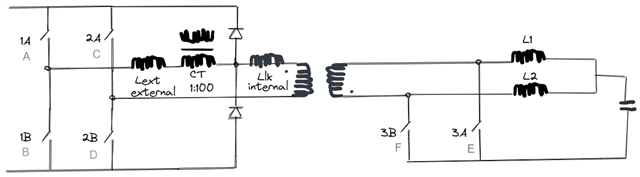

我在 Lext 上获得了以下不等电流波形。 顺便说一下、我使用二极管电桥来纠正 CT 电流的输出。

原理图如下所示。

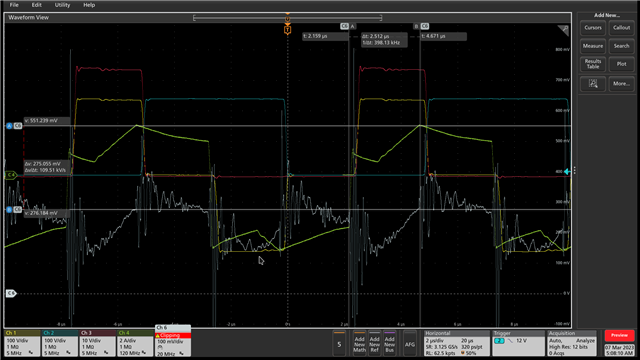

示波器颜色如下:

绿色:CT 上的电流、 灰色:ADC 信号- CT 的输出、

黄色:变压器的初级电压、 蓝色:2B VDS、

红色:3A VDS

波形1如下所示。

VIN=250 IIN=1.1 Vout=7.9 Iout=31.35、负载为 CR 模式= 0、25 Ω

波形2如下所示。

Vin=250 Iin=2.5 Vout=12.09 Iout=48.12、 CR 模式= 0、25 Ω

波形3如下所示、我移除了钳位二极管并获得以下波形。

VIN=250V、IIN=1.8、Vout=10.09、Iout=40、CR MODE = 0、25 Ω

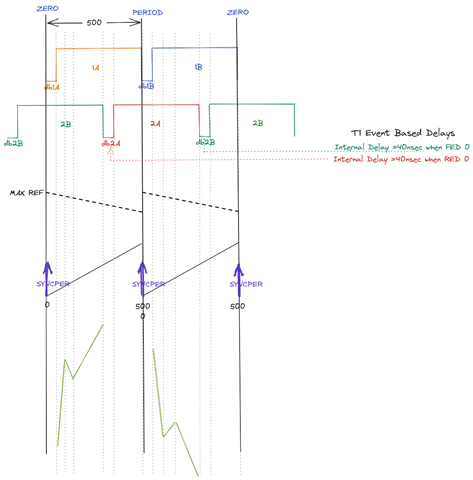

PWM8在全部为零时生成 SYNCPER 信号、并且我使用 PWM1和 PWM2驱动电源开关。

void SYNC_init(void)

{

SysCtl_setSyncOutputConfig(SYSCTL_SYNC_OUT_SRC_EPWM1SYNCOUT);

//

// For EPWM1, the sync input is: SYSCTL_SYNC_IN_SRC_EXTSYNCIN1

//

SysCtl_setSyncInputConfig(SYSCTL_SYNC_IN_EPWM4, SYSCTL_SYNC_IN_SRC_EPWM1SYNCOUT);

SysCtl_setSyncInputConfig(SYSCTL_SYNC_IN_EPWM7, SYSCTL_SYNC_IN_SRC_EPWM1SYNCOUT);

}

void InitHRPWM1(void)

{

EPWM_setPeriodLoadMode(EPWM1_BASE, EPWM_PERIOD_SHADOW_LOAD);

// Time-Base Submodule Configurations

EPWM_setClockPrescaler(EPWM1_BASE,EPWM_CLOCK_DIVIDER_1,EPWM_HSCLOCK_DIVIDER_1);

EPWM_setTimeBasePeriod(EPWM1_BASE, PeriodValue);

EPWM_setTimeBaseCounter(EPWM1_BASE, 0U);

EPWM_setTimeBaseCounterMode(EPWM1_BASE, EPWM_COUNTER_MODE_UP_DOWN);

//

// Phase Configuration and Set

// Configure PWM base1 as master

// SetPhaseShift as zero!

//

EPWM_disablePhaseShiftLoad(EPWM1_BASE);

EPWM_setPhaseShift(EPWM1_BASE, 0U);

EPWM_setSyncOutPulseMode(EPWM1_BASE, EPWM_SYNC_OUT_PULSE_ON_COUNTER_ZERO);

}

void InitHRPWM2(void)

{

// MISC. Period Load Mode

EPWM_setPeriodLoadMode(EPWM2_BASE, EPWM_PERIOD_SHADOW_LOAD);

// Time-Base Submodule Configurations

EPWM_setClockPrescaler(EPWM2_BASE,EPWM_CLOCK_DIVIDER_1,EPWM_HSCLOCK_DIVIDER_1);

EPWM_setTimeBasePeriod(EPWM2_BASE, PeriodValue);

EPWM_setTimeBaseCounter(EPWM2_BASE, 0U);

EPWM_setTimeBaseCounterMode(EPWM2_BASE, EPWM_COUNTER_MODE_UP_DOWN);

//

// Phase Configuration and Set

// Configure PWM base2 as slave

// SetPhaseShift = Value*TBCLK = Value*10nsec

//

EPWM_enablePhaseShiftLoad(EPWM2_BASE);

EPWM_setSyncOutPulseMode(EPWM2_BASE, EPWM_SYNC_OUT_PULSE_ON_EPWMxSYNCIN);

EPWM_setPhaseShift(EPWM2_BASE, 2); // Value*TBCLKs Phase-Shift is Set

EPWM_setCountModeAfterSync(EPWM2_BASE, EPWM_COUNT_MODE_UP_AFTER_SYNC);

}

void InitHRPWM8(void)

{

EPWM_setPeriodLoadMode(EPWM8_BASE, EPWM_PERIOD_SHADOW_LOAD);

// Time-Base Submodule Configurations

EPWM_setClockPrescaler(EPWM8_BASE,EPWM_CLOCK_DIVIDER_1,EPWM_HSCLOCK_DIVIDER_1);

EPWM_setTimeBasePeriod(EPWM8_BASE, PeriodValue -1);

EPWM_setTimeBaseCounter(EPWM8_BASE, 0);

EPWM_setTimeBaseCounterMode(EPWM8_BASE, EPWM_COUNTER_MODE_UP);

//

// Phase Configuration and Set

// Configure PWM base3 as slave

// SetPhaseShift = Value*TBCLK = Value*10nsec

EPWM_enablePhaseShiftLoad(EPWM8_BASE);

EPWM_setPhaseShift(EPWM8_BASE, 2); // Will be clarified later on!

EPWM_setSyncOutPulseMode(EPWM8_BASE, EPWM_SYNC_OUT_PULSE_ON_EPWMxSYNCIN);

EPWM_setCountModeAfterSync(EPWM8_BASE, EPWM_COUNT_MODE_UP_AFTER_SYNC);

HRPWM_setSyncPulseSource(EPWM8_BASE,HRPWM_PWMSYNC_SOURCE_ZERO);

}

void PSFB_HAL_initCmpssPCMC(void)

{

CMPSS_configHighComparator(CMPSS5_BASE,CMPSS_INSRC_DAC);

ASysCtl_selectCMPHPMux(ASYSCTL_CMPHPMUX_SELECT_5,0);

CMPSS_configDAC(CMPSS5_BASE, CMPSS_DACREF_VDDA |CMPSS_DACVAL_PWMSYNC | CMPSS_DACSRC_RAMP);

CMPSS_configRamp(CMPSS5_BASE,0,0,0U,8U,true);

CMPSS_initFilterHigh(CMPSS5_BASE);

CMPSS_configOutputsHigh(CMPSS5_BASE,

CMPSS_TRIP_ASYNC_COMP | CMPSS_TRIPOUT_ASYNC_COMP);

// Clear the latched comparator events

CMPSS_clearFilterLatchHigh(CMPSS5_BASE);

CMPSS_clearFilterLatchLow(CMPSS5_BASE);

// Enables the CMPSS module.

CMPSS_enableModule(CMPSS5_BASE);

DEVICE_DELAY_US(500);

您能否帮助您了解为什么 ADC 电压上的初级峰值电流电平不相等?

您可以调查我的相关软件行吗?