请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:TMS320F28384D 您好!

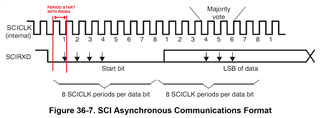

在下图中、我们展示了 SCI 通信格式。 我的客户有两个问题、

- SCI 开始采样前的延迟时间是多少?

- SCI 模块是否在 SCKCLK 上升沿对信号进行采样?

请告知您的评论、感谢您的帮助。

谢谢。此致、

Luke

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好!

在下图中、我们展示了 SCI 通信格式。 我的客户有两个问题、

请告知您的评论、感谢您的帮助。

谢谢。此致、

Luke

Luke、

感谢您的提问。

jin ma 说:SCI 开始采样前的延迟时间是多少?

SCI 应在起始位内的第一个完整 SCICLK 周期开始采样、但在检测到四个连续的零位内部 SCICLK 周期之前、不会将其作为有效的起始位计数。 请参阅 TRM 中的此节:

注意:如果一个 SCI ISR 仍在被处理、它可以在 ISR 完成前阻止采样。 这仅在 SCI 中断内、其他中断不会停止它。

jin ma 说:SCI 模块是否在 SCKCLK 上升沿对信号进行采样?

我相信它完成了从上升沿开始的一个完整的 SCICLK 周期。 但直到完成1个 SCICLK 周期后、才会算作"完整"样本。

我将与设计专家一起验证这是否正确:

您能否提供客户提出此问题的背景信息?

此致、

Vince