Other Parts Discussed in Thread: PMP23126, TIDM-02000, C2000WARE, LAUNCHXL-F280049C

主题中讨论的其他器件:PMP23126、 C2000WARE、 LAUNCHXL-F280049C

您好!

我使用 TIDM-02000和 PMP23126的示例代码实现了相移全桥的代码。 桥臂之间的相移由 PCMC 事件生成。

这是演示板 F280049C 上的台式测试。 我向 CMPS 高输入提供外部直流信号、并使用斜坡发生器来实现 PCMC。

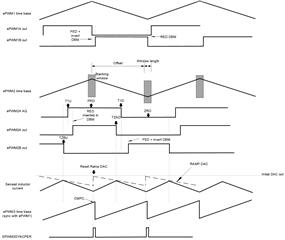

我生成了 ePWM8的2倍频率以便生成 SYNCPER 信号、从而使其同步。 EPWM 和 CMPSS。 我的主要 EPWM 是 EPWM1、2。 它们是同步的。 输入电压。

(我将 ePWM1、2、3、4用作 PWM 通道。 它们都是上-下计数模式。 ePWM5和6 -> SPI | ePWM7->UART | ePWM8 作为引导引脚配置。 引脚通过上拉电阻器连接到3.3V 电压。)

我可以获得%100占空比、而不会出现任何问题。 但是、在%0占空比时、EPWM 通道之间存在延迟。

我通过向 CMPSS 内部 DAC 提供较低的参考值来生成%0占空比。

我通过向 CMPSS 内部 DAC 提供更高的参考值来生成%100占空比。

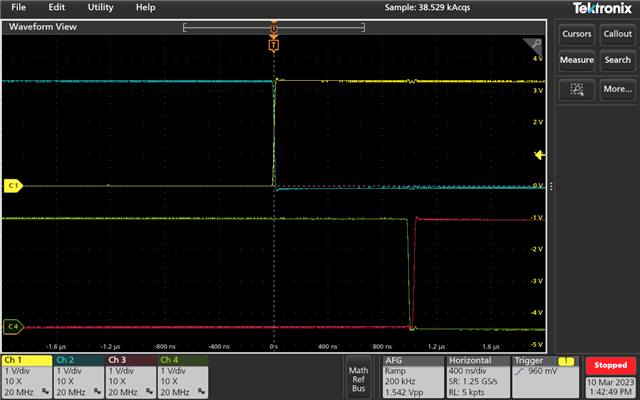

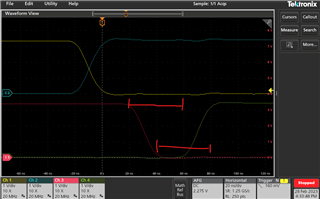

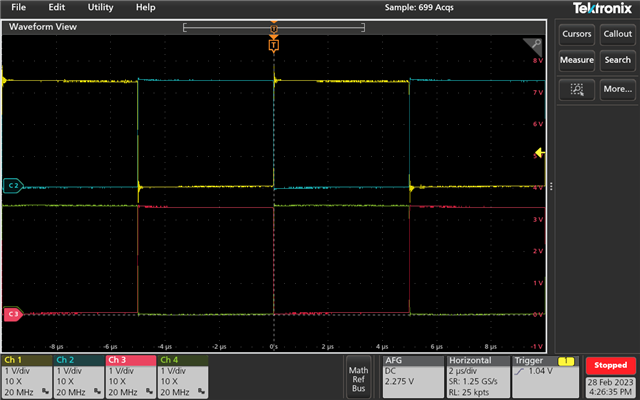

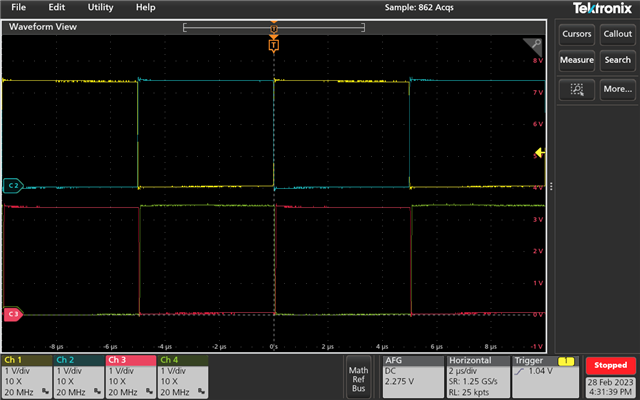

我按如下所示插入了波形。 黄色1A、蓝色1B、红色2A、绿色2B

PSFB 拓扑中%100占空比情况。 黄色和绿色上有%100匹配项! 为了查看性能、所有通道的死区均为0。

PSFB 拓扑中的%0占空比情况。 黄色和绿色有%0匹配! 为了查看性能、所有通道的死区均为0。

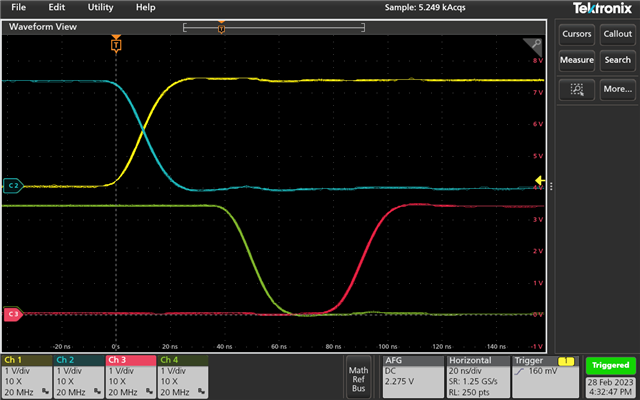

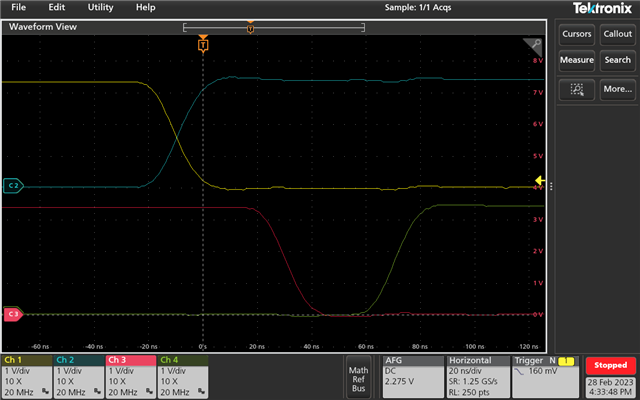

但是、开关之间的上升和下降时间之间存在延迟。

详情如下。

1) 1)您能解释一下我如何具有%100占空比、为什么不能具有%0占空比? 背后的现象是什么?

正如我回忆的那样,我在 CMPSS 上不使用任何滤波,而在跳匣区域使用消隐窗口。

同步 ePWM 时序中的电流链也可能是一个问题... 消隐可能是一个问题。。

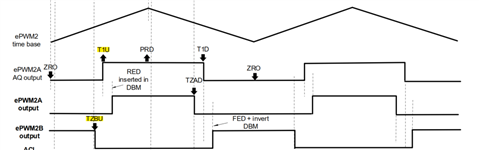

在 ePWM 跳闸处有消隐、如下所示。 如果需要、我可以提供更多信息。

// Set the blanking window offset in TBCLK counts

// An offset value in TBCLK counts is programmed

// which determines at what point after the CTR = PRD or CTR = 0 pulse the blanking window starts.

EPWM_setDigitalCompareWindowOffset(EPWM2_BASE, PeriodValue - 5);

// Set the blanking window length in TBCLK counts

// 10*TBLCK = 100nsec

EPWM_setDigitalCompareWindowLength(EPWM2_BASE, 10);