大家好

我们在某一产品的主板中使用 TSM320F28386D DSP、该产品还包括一个微处理器和一个 FPGA。 这里使用了两个 SPI 通道作为主设备与上行端口通信、每个通道的周期分别为4ms 和8ms。 两个通道都有两个 DMA 通道、一个用于 SIMO、另一个用于 SOMI、并以25Mbps 的波特率进行传输。

我们使用具有 DMA 支持的 SPI 通信来管理外设缓冲器。 每个 DMA 通道将在定义的突发次数完成后发布一个硬件中断、不过我们发现了这一点 随机地、4ms 周期 RX 中断不会弹出的时间的大约40% 。 相反、它在以下传输开始时调用、这似乎表明缺少一些帧、并且 DMA 传输仍在等待 最后一次突发。 然后、应用程序检测到 错误的 CRC 并执行恢复、为下一次传输做好准备。

一些注意事项:

- 与硬件的路径或电子产品一般是不在表,因为 DSP-up 通信工作正常在相同的条件下,在以前的版本。 此外、 将波特率减半没有影响 。

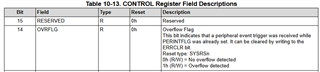

-两次传输之间的时间也大幅度增加,没有任何影响。 此外、我们还通过调试和 GPIO 检查了这一点 溢出不会发生 。

- 关闭优化后、问题似乎得到了解决 。 0级优化用于发生故障的版本和以前的版本。 在大多数情况下、关闭 SPI 驱动程序源文件的优化就足够了、但有时需要从其余驱动程序中删除优化、具体取决于应用程序代码中的内容。 不能选择不使用优化、因为必须使用内联。

- DMA 转储中涉及的所有变量均定义为 volatile。

- SPI 缓冲区管理中使用的所有4个 DMA 通道也用于在传输结束时在变量之间执行1/2一次性内存转储。 转储完成后、它们会被重新配置为 当主器件(UP)开始通信时管理 SPI 缓冲区。 由于我们已检查为下一次传输准备 DMA 通道的功能 是否在开始之前就已成功实现(没有溢出)、因此这不应导致性能故障。

-禁用内联对故障没有影响。 也没有使用--aliased_variables 参数。

-使用的 CCS 版本为12.1.0.00007,编译器版本为 TI v22.6.0.LTS

我们一直在查看"优化 C/C++编译器用户指南"、但到目前为止没有任何效果。 任何类型的建议都将非常感谢。 提前感谢!