Thread 中讨论的其他器件:SysConfig、 C2000WARE

我在中断模式下使用 SCI。 无 FIFO。

当我接收到 charachter (8位、9600波特、无奇偶校验、1个停止位)时、我获得了中断。 在中断例程中、我将字符从缓冲区中拉出、并将其放入我自己的 RXBuf 中、以将消息标空。 我一直在寻找一个 作为终止字符、因此我可以设置一个标志、告知主例程有一条消息就绪。 这种技术已经使用了40年左右、广泛用于各种处理器。 其中包括2406和28069。 非常基本的东西。

如果我使用超级终端等终端程序、并一次发送一个字符的消息、一切都很顺利。 我命中时、字节将放入接收缓冲区 对消息进行解码并执行相应操作。

问题:

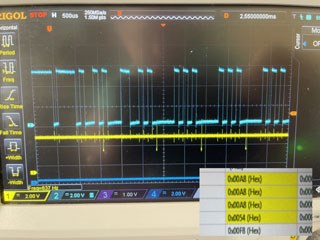

如果我使用我的应用程序(已经使用它20多年了)、它允许我单击一次发送整个消息、中断仍然会发生在每个 charater 上、但280025 RXBUF 产生的结果是巨大的。 输出的字节与正在输入的字节不匹配。 这就好像字符尚未完全移入缓冲区一样。 很自然、我的应用程序产生的字节一个接一个地出现、但正确的起始位和停止位也存在、因此它不应该是计时数据。

知道这家伙在干什么吗?

一如既往,所有精彩的建议和愚蠢的想法欢迎...