主题中讨论的其他器件:UNIFLASH、 C2000WARE、 SysConfig、 TMS320F280039C

您好!

有时、我很难让 F280034以独立模式运行。 我先介绍 LAUNCHXL_F280039电路板。 代码将在此运行、从闪存引导时不会出现问题。 我曾尝试使用 F280034改用定制电路板。 我更新了比较器文件、因为它从0034开始、从0x88000开始、在0039开始、从0x80000:

/*

//###########################################################################

//

// FILE: F280034_flash_lnk.cmd

//

// TITLE: Linker Command File For F280034 Device

//

//###########################################################################

*/

MEMORY

{

BOOT_RSVD : origin = 0x00000002, length = 0x00000126

RAMM0 : origin = 0x00000128, length = 0x000002D8

RAMM1 : origin = 0x00000400, length = 0x000003F8 /* on-chip RAM block M1 */

// RAMM1_RSVD : origin = 0x000007F8, length = 0x00000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

RAMLS0 : origin = 0x00008000, length = 0x00000800

RAMLS1 : origin = 0x00008800, length = 0x00000800

RAMLS2 : origin = 0x00009000, length = 0x00000800

RAMLS3 : origin = 0x00009800, length = 0x00000800

RAMLS4 : origin = 0x0000A000, length = 0x00000800

RAMLS5 : origin = 0x0000A800, length = 0x00000800

RAMLS6 : origin = 0x0000B000, length = 0x00000800

RAMLS7 : origin = 0x0000B800, length = 0x00000800

/* Combining all the LS RAMs */

//RAMLS : origin = 0x00008000, length = 0x00004000

RAMGS0 : origin = 0x0000C000, length = 0x00001000

RAMGS1 : origin = 0x0000D000, length = 0x00001000

RAMGS2 : origin = 0x0000E000, length = 0x00001000

RAMGS3 : origin = 0x0000F000, length = 0x00000FF8

// RAMGS3_RSVD : origin = 0x000FFF8, length = 0x00000008 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

BOOTROM : origin = 0x003F8000, length = 0x00007FC0

SECURE_ROM : origin = 0x003F2000, length = 0x00006000

RESET : origin = 0x003FFFC0, length = 0x00000002

/*

#ifdef __TI_COMPILER_VERSION__

#if __TI_COMPILER_VERSION__ >= 20012000

#endif

#endif

*/

BEGIN : origin = 0x00088000, length = 0x00000002

/* Flash sectors */

/* BANK 0 */

FLASH_BANK0_SEC0 : origin = 0x088002, length = 0x000FFE

FLASH_BANK0_SEC1 : origin = 0x089000, length = 0x001000

FLASH_BANK0_SEC2 : origin = 0x08a000, length = 0x001000

FLASH_BANK0_SEC3 : origin = 0x08b000, length = 0x001000

FLASH_BANK0_SEC4 : origin = 0x08c000, length = 0x001000

FLASH_BANK0_SEC5 : origin = 0x08d000, length = 0x001000

FLASH_BANK0_SEC6 : origin = 0x08e000, length = 0x001000

FLASH_BANK0_SEC7 : origin = 0x08f000, length = 0x000FF0

FLASH_BANK0_SEC7_DO_NOT_USE : origin = 0x08FFF0, length = 0x000010 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

/* BANK 1 */

FLASH_BANK1_SEC0 : origin = 0x090000, length = 0x001000

FLASH_BANK1_SEC1 : origin = 0x091000, length = 0x001000

FLASH_BANK1_SEC2 : origin = 0x092000, length = 0x001000

FLASH_BANK1_SEC3 : origin = 0x093000, length = 0x001000

FLASH_BANK1_SEC4 : origin = 0x094000, length = 0x001000

FLASH_BANK1_SEC5 : origin = 0x095000, length = 0x001000

FLASH_BANK1_SEC6 : origin = 0x096000, length = 0x001000

FLASH_BANK1_SEC7 : origin = 0x097000, length = 0x000FF0

FLASH_BANK1_SEC7_DO_NOT_USE : origin = 0x097FF0, length = 0x000010 /* Reserve and do not use for code as per the errata advisory "Memory: Prefetching Beyond Valid Memory" */

/*

#ifdef __TI_COMPILER_VERSION__

#if __TI_COMPILER_VERSION__ >= 20012000

} crc(_ccs_flash_checksum, algorithm=C28_CHECKSUM_16)

#endif

#endif

*/

}

SECTIONS

{

codestart : > BEGIN, ALIGN(8)

.text : >> FLASH_BANK0_SEC2 | FLASH_BANK0_SEC3 | FLASH_BANK0_SEC4, ALIGN(8)

.cinit : > FLASH_BANK0_SEC1, ALIGN(8)

.switch : > FLASH_BANK0_SEC1, ALIGN(8)

.reset : > RESET, TYPE = DSECT /* not used, */

.stack : > RAMM1

#if defined(__TI_EABI__)

.init_array : > FLASH_BANK0_SEC1, ALIGN(8)

.bss : > RAMLS5

.bss:output : > RAMLS3

.bss:cio : > RAMLS0

.data : > RAMLS5

.sysmem : > RAMLS5

.const : > FLASH_BANK0_SEC4, ALIGN(8)

#else

.pinit : > FLASH_BANK0_SEC1, ALIGN(8)

.ebss : > RAMLS5

.esysmem : > RAMLS5

.cio : > RAMLS0

.econst : > FLASH_BANK0_SEC4, ALIGN(8)

#endif

ramgs0 : > RAMGS0

ramgs1 : > RAMGS0

/* Allocate IQ math areas: */

IQmath : > FLASH_BANK0_SEC1, ALIGN(8)

IQmathTables : > FLASH_BANK0_SEC2, ALIGN(8)

.TI.ramfunc : LOAD = FLASH_BANK0_SEC1,

RUN = RAMLS0,

LOAD_START(RamfuncsLoadStart),

LOAD_SIZE(RamfuncsLoadSize),

LOAD_END(RamfuncsLoadEnd),

RUN_START(RamfuncsRunStart),

RUN_SIZE(RamfuncsRunSize),

RUN_END(RamfuncsRunEnd),

ALIGN(8)

/* crc/checksum section configured as COPY section to avoid including in executable */

.TI.memcrc : type = COPY

}

/*

//###########################################################################

// End of file.

//###########################################################################

*/

之后我做的是调整 GEL 文件。 随 CCS 提供的文件未针对起始地址0x88000进行调整、并且我无法使用 X110调试器进行闪存。 在投诉地址0x80000不可用或类似的东西。 我更换了

...

GEL_MapAddStr(0x00080000,0, 0x10000, "R|AS2",0); /* FLASH BANK0 (128 KBytes) */

...

GEL_MapAddStr(0x00080000,1, 0x10000, "R|AS2",0); /* FLASH BANK0 (64 KBytes) */

GEL_MapAddStr(0x00090000,1, 0x10000, "R|AS2",0); /* FLASH BANK1 (64 KBytes) */

GEL_MapAddStr(0x01080000,1, 0x2000, "R|AS2",0); /* FLASH BANK0 ECC (16 KBytes) */

GEL_MapAddStr(0x01082000,1, 0x2000, "R|AS2",0); /* FLASH BANK0 ECC (16 KBytes) */

...

替换为这一个:

...

GEL_MapAddStr(0x00088000,0, 0x10000, "R|AS2",0); /* FLASH BANK0 (128 KBytes) */

...

GEL_MapAddStr(0x00088000,1, 0x8000, "R|AS2",0); /* FLASH BANK0 (64 KBytes) */

GEL_MapAddStr(0x00090000,1, 0x8000, "R|AS2",0); /* FLASH BANK1 (64 KBytes) */

GEL_MapAddStr(0x01081000,1, 0x1000, "R|AS2",0); /* FLASH BANK0 ECC (16 KBytes) */

GEL_MapAddStr(0x01082000,1, 0x1000, "R|AS2",0); /* FLASH BANK0 ECC (16 KBytes) */

...

刷写后、代码使用调试器正常运行。 第一行中的"codestart"部分

WD_DISABLE .set 1 ;set to 1 to disable WD, else set to 0

因此在到达我的代码后、应立即禁用看门狗。 但当我断开调试器并进行硬件复位时、微控制器开始复位。 GPIO24和 GPIO32这两个引脚都设置为高电平、我并不期待硬件问题、电路板已经过验证、硬件也按预期工作(我仍然尝试了2个电路板、只是为了确保在某个地方没有硬件问题)。 因此 MCU 应该从闪存引导。 但在 XRS 引脚上、我可以看到大约每20ms 50us 的周期性脉冲、如下图所示。 这看起来像是看门狗复位、但我无法完全确定。 该引脚在另一侧为"漏极开路"、因此另一侧的元件不应对该 MCU 的行为产生任何影响。

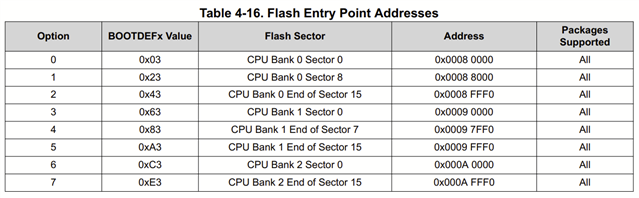

从那时起,我尝试了许多不同的东西。 我已在调试器设置中勾选"自动 ECC 生成"、并且我可以在 ECC 存储器中看到一些数据。 ECC 看起来就在那里。然后、我发现、如果以这种方式配置 BootROM、它可能会跳转到闪存的入口地址(就像我在本例中那样)。 但是、可能默认的选项0是地址0x80000 (检查下图)、因此我认为必须在 OTP 中写入、我希望入口点为0x88000。

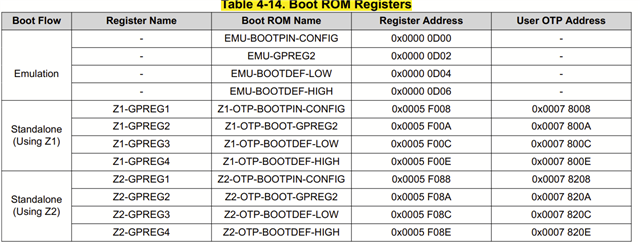

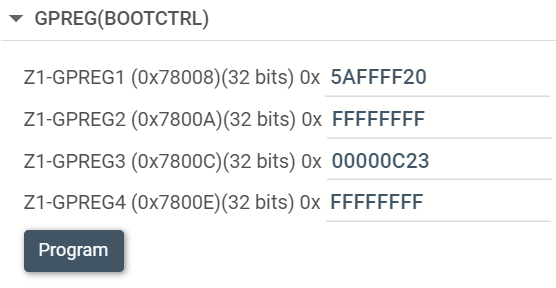

所以我想写0x78008 --> 0x5AFFFF20、这样它的启动只依赖于 GPIO32。 以及在0x7800C --> 0x00000C23中。 第一个选项是从地址0x88000的闪存引导、第二个选项是从 SPI 闪存引导。

我无法写入 OTP。 我曾尝试在代码中添加这一点、但无法使用 FAPI 代码使其正确编译。 然后、我尝试将其添加到链接器文件中、但未刷写。 我可以在"out"文件中看到该地址处的数据(实际上在 hex2000生成的 S19文件中进行检查)、但如果我使用 XDS110刷写该映像、然后使用"存储器浏览器"进行检查、我在此地址只能看到0xFF。 然后、我在 Uniflash 尝试了相同的方法、同样失败了。 然后、我已在 CCS 和 Uniflash 中尝试手动写入这些寄存器、如下所示。

我从 CCS 和 Uniflash 都得到的错误是:

因为这是第一个定制板、我想 OTP 可能是在无意之前写入的并且已经锁定(即使它在所有这些寄存器中的值为0xFF)。 然后、我采用了同类型的另一个定制板、并且不刷写任何软件、只需读取存储器以确保它是新的、然后直接写入这些 OTP 寄存器、它也以同样的方式失败。

我的想法快用完了。 有人知道问题可能出在哪里吗? 我是否完全需要刷写0034的 OTP 以使其跳至0x88000、或者这是此 MCU 上的默认入口点? 为什么在 XRS 引脚上看到此复位? 这是什么呢? 我的假设是、我的代码根本没有执行、它会在到达之前被重置。

谢谢你