大家好、

以下是客户可能需要您的帮助的问题:

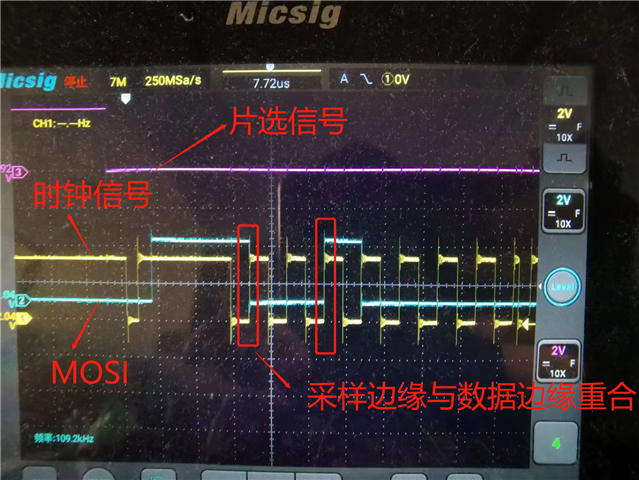

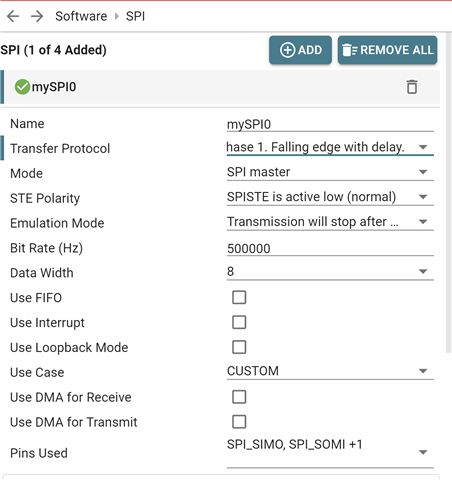

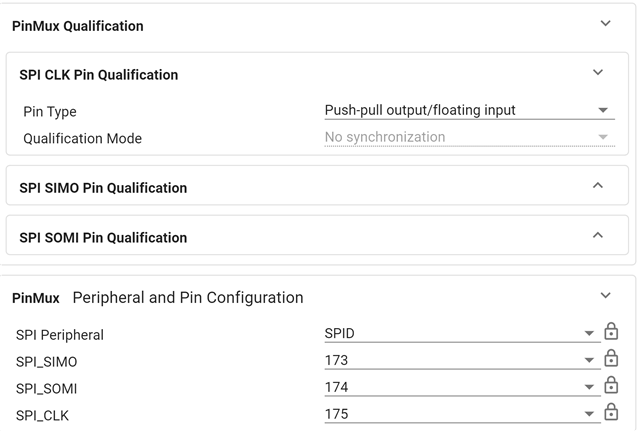

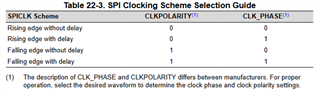

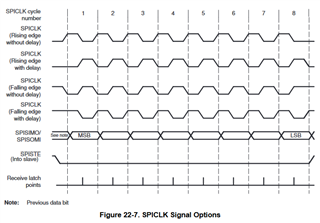

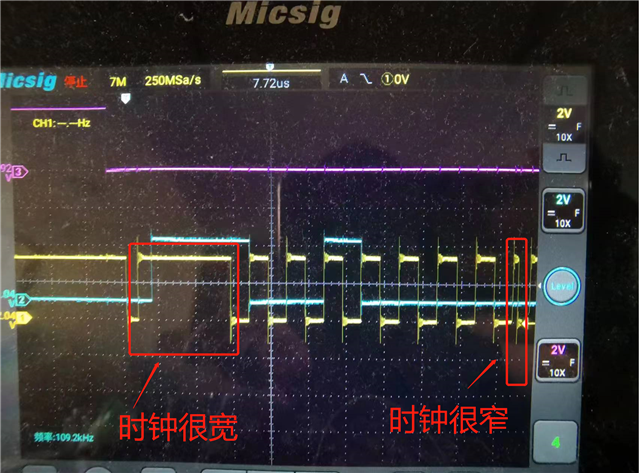

使用 syscfg 工具配置生成以下 SPI 初始化代码以访问 SPI 串行闪存。 读取器件 ID 时、向闪存发送0x90命令。 测量波形如下图所示:

发现 DSP 芯片生成的波形时钟本质上与 MOSI 线路的边沿对齐、导致无法正确读取器件 ID。

因此、客户想知道是否有任何可用于优化波形的初始化配置?

void mySPI0_init (){

SPI_disableModule (mySPI0_BASE);

SPI_setConfig (mySPI0_BASE、DEVICE_LSPCLK_FREQ、SPI_PROT_POL1PHA1、

SPI_MODE_MASTER、500000、8);

SPI_disableFIFO (mySPI0_BASE);

SPI_disableLoopback (mySPI0_BASE);

SPI_setEmulationMode (mySPI0_BASE、SPI_emulation_stop_fter_transmit);

SPI_enableModule (mySPI0_BASE);

}

您能帮助检查这个问题吗? 谢谢。

此致、

樱桃

(红色块表示宽时钟和窄时钟)

(红色块表示宽时钟和窄时钟)