Other Parts Discussed in Thread: SYSCONFIG, C2000WARE

Thread 中讨论的其他器件:SysConfig、 C2000WARE

大家好

我将使用 DB 模块生成互补 ePWM、但希望在 EPWM1B 输出到引脚之前对其进行修改。 为了让问题简单易行、在逻辑块中、我刚才进行了"与"运算

输入 i0信号(EPWM1B)的值为1。 如果我 根据下表将 CLB 覆盖设置为输出2 (EPWM1B)、 那么当我只需要 A 时、我获取的是 EPWM1B 引脚上出现的连续低电平

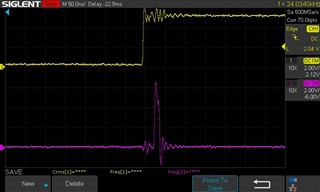

原始输入 EPWM1B 信号的副本。 如果我将覆盖项设置为输出0、EPWM1A 引脚也会变为低电平、但看到与 EPWM1B 转换相匹配的良好脉冲。 随附屏幕截图。

如果我没有分配覆盖输出、则 EPWM1A 和1B 在相应引脚上显示为"不变"PWM。

作为

最终、我需要使用 CMPSS1来修改 EPWM1B、如下面的 CLB 设置所示。 这可能发生在 TZ 模块之前或之后、因为我只对这两个信号进行与操作。 但我不能

甚至在忽略我分配给 CMPSS1的 i1 (AUXSIG0)时让它运行。 我 在交叉输出上广泛复制了 clb_ex12、但看不到我出错了。

我会 注意到、我 在不使用 SysConfig 的情况下设置 EPWM1和 CMPSS1、而是直接使用 driverlib。

有人能看出我可能做错了什么吗?

谢谢

Andrew