Other Parts Discussed in Thread: CCSTUDIO, UNIFLASH

主题中讨论的其他器件:CCStudio、 UNIFLASH

大家好!

在最初刷写 F28384D 的 CPU1后、我们会遇到问题。 他似乎不知道该怎么说。

配置:

系统时钟:50MHz (使用 10MHz 内部振荡器:INT_OSC2)

编程方法:

CCS12或 Matlab 代码生成(C2000)

调试程序:

XDS110的一个示例

我已经对 CPU1和 CPU2进行了编程。 我可以更改 CPU2闪存程序、但对于 CPU1、我只能对 RAM 进行编程。

我收到的错误:

已构建1个模型中的0个(1个模型已更新)

构建持续时间:0h 0m 33.968s

部署到硬件板时出现以下错误:

调试服务器脚本编写(DSS)错误:

***用户输入:

目标配置:C:\PROGRA~3\MATLAB\suppor~1\R2022a\toolbox\target\suppor~1\tic2000\ccs_CO~1\jams_~1.CCX

程序名称:C:\SY6632~1\SON84~2.out

板名称:*

CPU 名称:C28xx_CPU1

硬件名称:TI_F2838x_(C28x)

从闪存引导:1.

***正在启动调试会话...

C28xx_CPU1:GEL 输出:

存储器映射初始化完成

C28xx_CPU1:GEL 输出:

... DCSM 初始化开始...

C28xx_CPU1:GEL 输出:

... DCSM 初始化完成...

C28xx_CPU1:GEL 输出:

CPU2已退出复位并配置为等待引导。

(如果您以前已连接、可能必须恢复 CPU2才能到达等待引导循环。)

C28xx_CPU1:GEL 输出:

CM 已退出复位并配置为等待引导。

(如果您之前已连接、可能必须恢复 CM 才能到达等待引导循环。)

C28xx_CPU1:如果在一个内核上完成擦除/编程(E/P)操作、另一个内核不应从共享 RAM (SR)中执行、因为它们用于 E/P 代码。 可以在两个闪存组都编程后从 SR 开始执行用户代码。

C28xx_CPU1:只有 CPU1片上闪存插件可以为 CPU1、CPU2和 CM 闪存操作配置时钟。 当调用 CPU1闪存操作时、插件会自动配置 PLL。 但是、如果用户只想执行 CPU2或 CM 闪存操作、而不在当前会话中执行先前的 CPU1操作、则应在调用 CPU2和 CM 闪存操作之前点击 CPU1的片上闪存插件中的"配置时钟"按钮。 使用此按钮时、闪存插件会将 CPU1/CPU2的时钟配置为190MHz、将 CM 配置为95MHz 并使用 INTOSC2作为时钟源。 插件将保持这样的 PLL 配置、用户应用应根据应用的要求配置 PLL。

C28xx_CPU2:GEL 输出:

存储器映射初始化完成

C28xx_CPU2:如果在一个内核上完成擦除/编程(E/P)操作、则另一个内核不应从共享 RAM (SR)执行、因为它们用于 E/P 代码。 可以在两个闪存组都编程后从 SR 开始执行用户代码。

C28xx_CPU2:只有 CPU1片上闪存插件可以为 CPU1、CPU2和 CM 闪存操作配置时钟。 当调用 CPU1闪存操作时、插件会自动配置 PLL。 但是、如果用户只想执行 CPU2或 CM 闪存操作、而不在当前会话中执行先前的 CPU1操作、则应在调用 CPU2和 CM 闪存操作之前点击 CPU1的片上闪存插件中的"配置时钟"按钮。 使用此按钮时、闪存插件会将 CPU1/CPU2的时钟配置为190MHz、将 CM 配置为95MHz 并使用 INTOSC2作为时钟源。 插件将保持这样的 PLL 配置、用户应用应根据应用的要求配置 PLL。

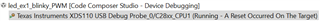

***调试会话名称:Texas Instruments XDS110 USB Debug Probe_0/C28xx_CPU1

***电路板名称:Texas Instruments XDS110 USB Debug Probe_0

*** CPU 名称:C28xx_CPU1

***连接至目标...

严重:未找到选项

***警告:此 CCS 版本不支持时钟备份和恢复功能。 使用"从闪存引导"时、在刷写后执行电路板下电上电、以确保程序以所需的时钟频率执行。

C28xx_CPU1:GEL 输出:

... DCSM 初始化开始...

C28xx_CPU1:GEL 输出:

... DCSM 初始化完成...

C28xx_CPU1:GEL 输出:

CPU2已退出复位并配置为等待引导。

(如果您以前已连接、可能必须恢复 CPU2才能到达等待引导循环。)

C28xx_CPU1:GEL 输出:

CM 已退出复位并配置为等待引导。

(如果您之前已连接、可能必须恢复 CM 才能到达等待引导循环。)

***将程序加载到目标中...

C28xx_CPU1:GEL 输出:

... DCSM 初始化开始...

C28xx_CPU1:GEL 输出:

... DCSM 初始化完成...

C28xx_CPU1:GEL 输出:

CPU2已退出复位并配置为等待引导。

(如果您以前已连接、可能必须恢复 CPU2才能到达等待引导循环。)

C28xx_CPU1:GEL 输出:

CM 已退出复位并配置为等待引导。

(如果您之前已连接、可能必须恢复 CM 才能到达等待引导循环。)

C28xx_CPU1:GEL 输出:

... DCSM 初始化开始...

C28xx_CPU1:GEL 输出:

... DCSM 初始化完成...

C28xx_CPU1:GEL 输出:

CPU2已退出复位并配置为等待引导。

(如果您以前已连接、可能必须恢复 CPU2才能到达等待引导循环。)

C28xx_CPU1:GEL 输出:

CM 已退出复位并配置为等待引导。

(如果您之前已连接、可能必须恢复 CM 才能到达等待引导循环。)

严重:C28xx_CPU1:在0xd148上执行"保持暂停"操作时在删除断点时出现问题:(ERROR -1066 @ 0xD148)无法设置/清除请求的断点。 验证断点地址是否在有效的存储器中。 (仿真包9.5.0.00143)

严重:C28xx_CPU1:执行 PLL 配置算法时出错。 操作已取消。 (0x0)

严重:C28xx_CPU1:文件加载程序:内存写入失败:未知错误

严重:C28xx_CPU1:GEL:文件:C:\SY6632~1\SNA84~2.out:加载失败。

严重:文件:C:\SY6632~1\SON84~2.Out:加载失败。

严重:加载"C:\SY6632~1\SON84~2.out"时出错:文件:C:\SY6632~1\SON84~2.out:加载失败。

org.mozilla.javascript.WrappedException:packed com.ti.ccstudio.scripting.environment.ScriptingException:错误加载"C:\SY6632~1\SONA84~2.out":文件:C:\SY6632~1\SONA84~2.out:加载失败。 (C:\PROGRA~3\MATLAB\suppor~1\R2022a\toolbox\shared\suppr~1\tic2000/CCS_CO~1/RUNPRO~1.JS#169)

网址为 org.mozilo.javascript.context.throwAsScriptRuntimeEx(context.java:1693)

请访问 org.mozilla.javascript.MemberBox.invoke(MemberBox.java:160)

请访问 org.mozilla.javascript.NativeJavaMethod.call(NativeJavaMethod.java:204)

请访问 org.mozilla.javascript.optimizer.OptRuntime.call1(OptRuntime.java:66)

at org.mozilo.javascript.gen.c1._c0 (C:\PROGRA~3\MATLAB\suppr~1\R2022a\toolbox\shared\suppr~1\tic2000/CCS_CO~1/RUNPRO~1.JS:169)

请访问 org.mozilla.javascript.gen.c1.call(C:\PROGRA~3\MATLAB\SUPPOR~1\R2022a\toolbox\shared\SUPPOR~1\tic2000/CCS_CO~1/RUNPRO~1.JS)

at org.mozilo.javascript.ContextFactory.doTopCall (ContextFactory.java:340)

网址为 org.mozilla.javascript.ScriptRuntime.doTopCall (ScriptRuntime.Java:2758)

请访问 org.mozilla.javascript.gen.c1.call(C:\PROGRA~3\MATLAB\SUPPOR~1\R2022a\toolbox\shared\SUPPOR~1\tic2000/CCS_CO~1/RUNPRO~1.JS)

at org.mozilla.javascript.gen.c1.exec (C:\PROGRA~3\MATLAB\suppr~1\R2022a\toolbox\shared\suppr~1\tic2000/CCS_CO~1/RUNPRO~1.JS)

网址为 org.mozilla.javascript.tools.shell.Main.evaluateScript (Main.Java:503)

请访问 org.mozilla.javascript.tools.shell.Main.processFileSecure(Main.java:425)

请访问 org.mozilla.javascript.tools.shell.Main.processFile(Main.java:391)

请访问 org.mozilla.javascript.tools.shell.Main.processSource(Main.java:382)

请访问 org.mozilla.javascript.tools.shell.Main.processFiles(Main.java:179)

网址为 org.mozilla.javascript.tools.shell.Main$IProxy.run(Main.java:100)

请访问 org.mozilla.javascript.Context.call(Context.java:528)

请访问 org.mozilla.javascript.ContextFactory.call(ContextFactory.java:450)

位于 org.mozilla.javascript.tools.shell.Main.exec(Main.java:162)

请访问 com.ti.ccstudio.apps.internal.scripting.RunScript$1.run(RunScript.java:89)

由于:com.ti.ccstudio .scripting.environment.ScriptingException:错误加载"C:\SY6632~1\SONA84~2.out":文件:C:\SY6632~1\SONA84~2.out:加载失败。

请访问 com.ti.debug.engine.scripting.Memory.loadProgram(Memory.java:932)

位于 java.base/jdk.internal.reflect.NativeMethodAccessorImpl.invoke0(Native 方法)

位于 java.base/jdk.internal.reflect.NativeMethodAccessorImpl.invoke(Unknown 源代码)

位于 java.base/jdk.internal.reflect.DelegatingMethodAccessorImpl.invoke(Unknown 源代码)

位于 java.base/java.lang.reflect.Method.invoke(Unknown 源代码)

请访问 org.mozilla.javascript.MemberBox.invoke(MemberBox.java:145)

... 18更多

严重:C28xx_CPU1:在0xd058处的操作"保持停止"设置断点时出现问题:(ERROR -1066 @ 0xD058)无法设置/清除请求的断点。 验证断点地址是否在有效的存储器中。 (仿真包9.5.0.00143)

警告:C28xx_CPU1:断点管理器:重试一个 AET 断点

感谢您的支持。