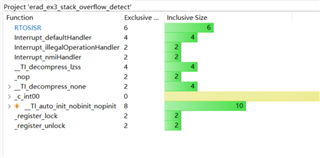

当使用 TI 的示例时:erad_ex3_stack_overflow_detect

文件中的所有表格

RAMM1. : origin = 0x000400, length = 0x0003F8 /*片上 RAM 块 M1 */

.stack :> RAMM1.

长度为 0x0003F8 (1016 *2= 2032字节)

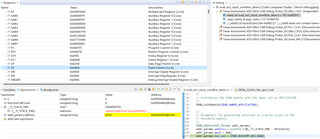

我假设 addr_params.address 应是2032-10=2022。

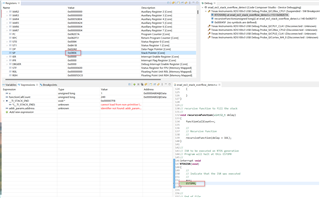

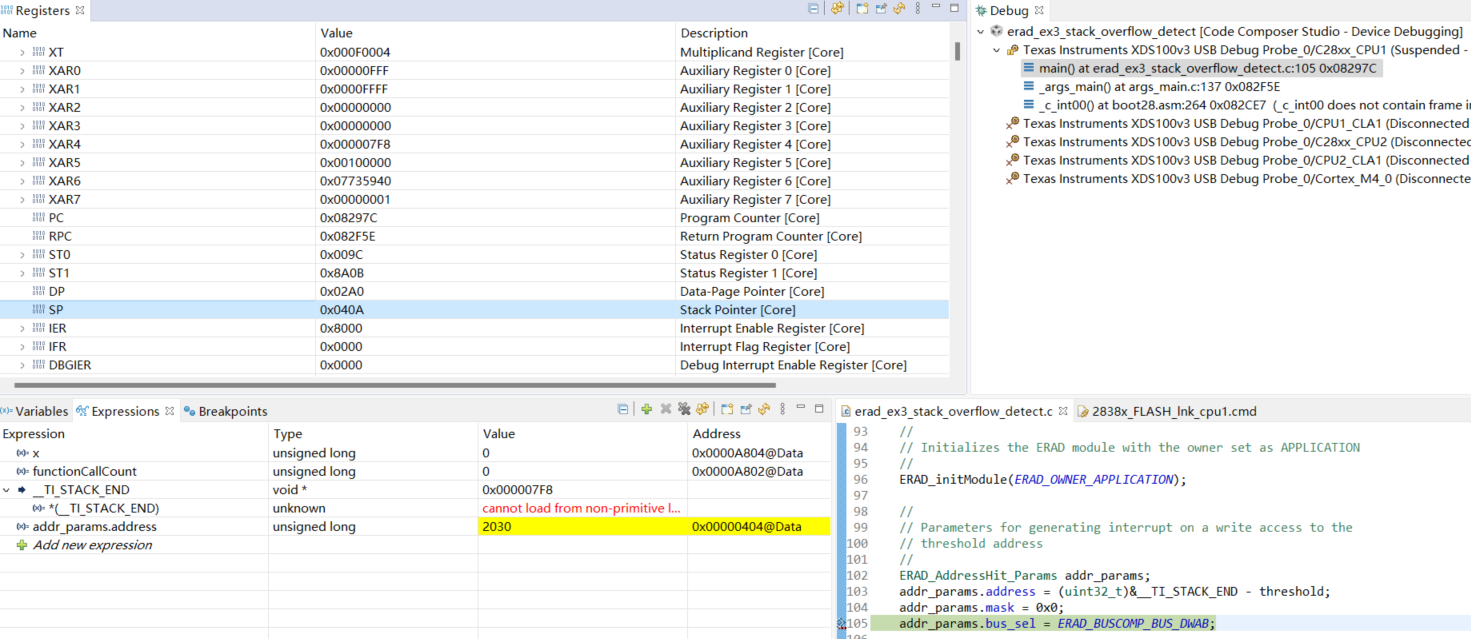

但正如下面的调试窗口显示的、该值为2030。

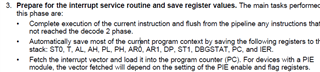

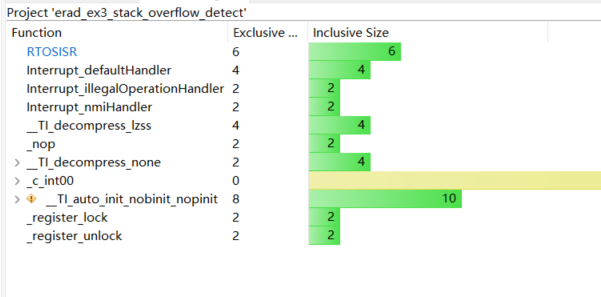

另一个问题是、当首次进入 RTOSISR 中断时。

获取上述调试信息、 addr_params.addres =2030 (3F7)

堆栈的起始地址为 0x000400。

因此、我想当 SP 大于0x400+0x3F7时、它将进入 RTOSISR 中断。

我想当 首次进入 RTOSISR 中断时、SP 值应为0X7F7+0x06=0X7FD。 而不是0x806。

一定是与我的理解不符的事情。

HOEP TI 专家可以为您提供帮助